TMP92CZ26A

92CZ26A-425

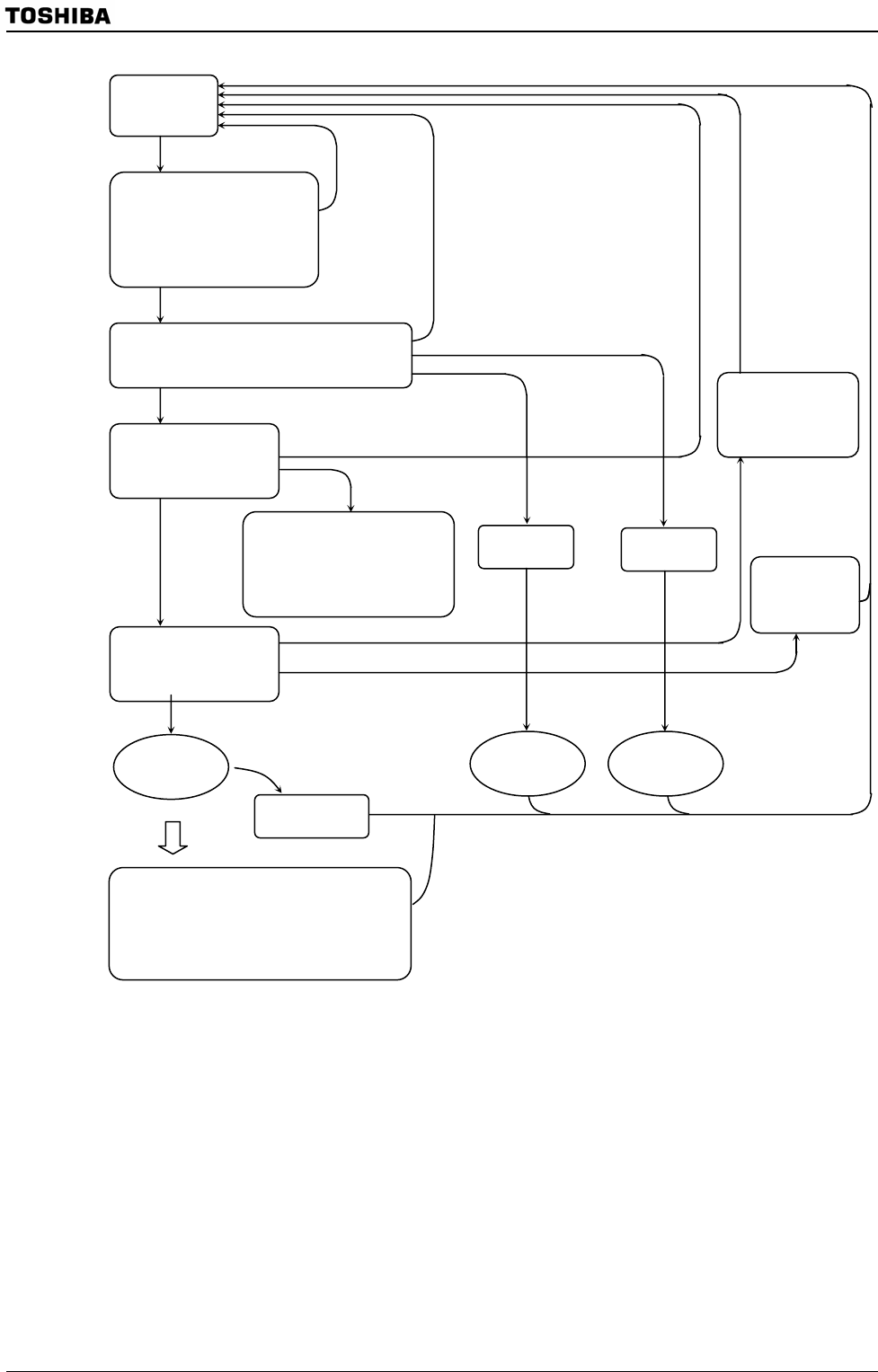

Figure 3.16.8 Control Flow in UDC (Bulk transfer type (Receiving))

IDLE

Receive OUT token

Confirm Status

• Confirm STATUS register (status)

• Confirm FIFO’s condition

OK

OK

OK

Transmit ACK

Toggle error

• Set STATU Sat RX_ERR

• Put back FIFO address

pointer

• Retry recognition clean

data

Confirm Token packet

• PID

• Address

• Endpoint

• Transfer mode

• Error

Transmit NAK Transmit STALL

Invalid

Stall

FIFO em

p

t

y

Except data PID

Time out

Erro

r

Generate DATA PID

• DATA0/DATA1

• Time out

• Toggle check

Receive data

• Error

• Confirm receiving data

number

Error transaction

• Set STATUS at

RX_ERR

• Put back FIFO

address pointer

Cancel data

Cancel data

Error

transaction

• Set status to

stall

Data communication of

more than payload

Retry transaction

OK

Normal finish transaction

• Set transfer data number to DATASIZE

register

• Set DATASET register

• Renew toggle bit

• Set STATUS to DATAIN

OK