TMP92CZ26A

92CZ26A-530

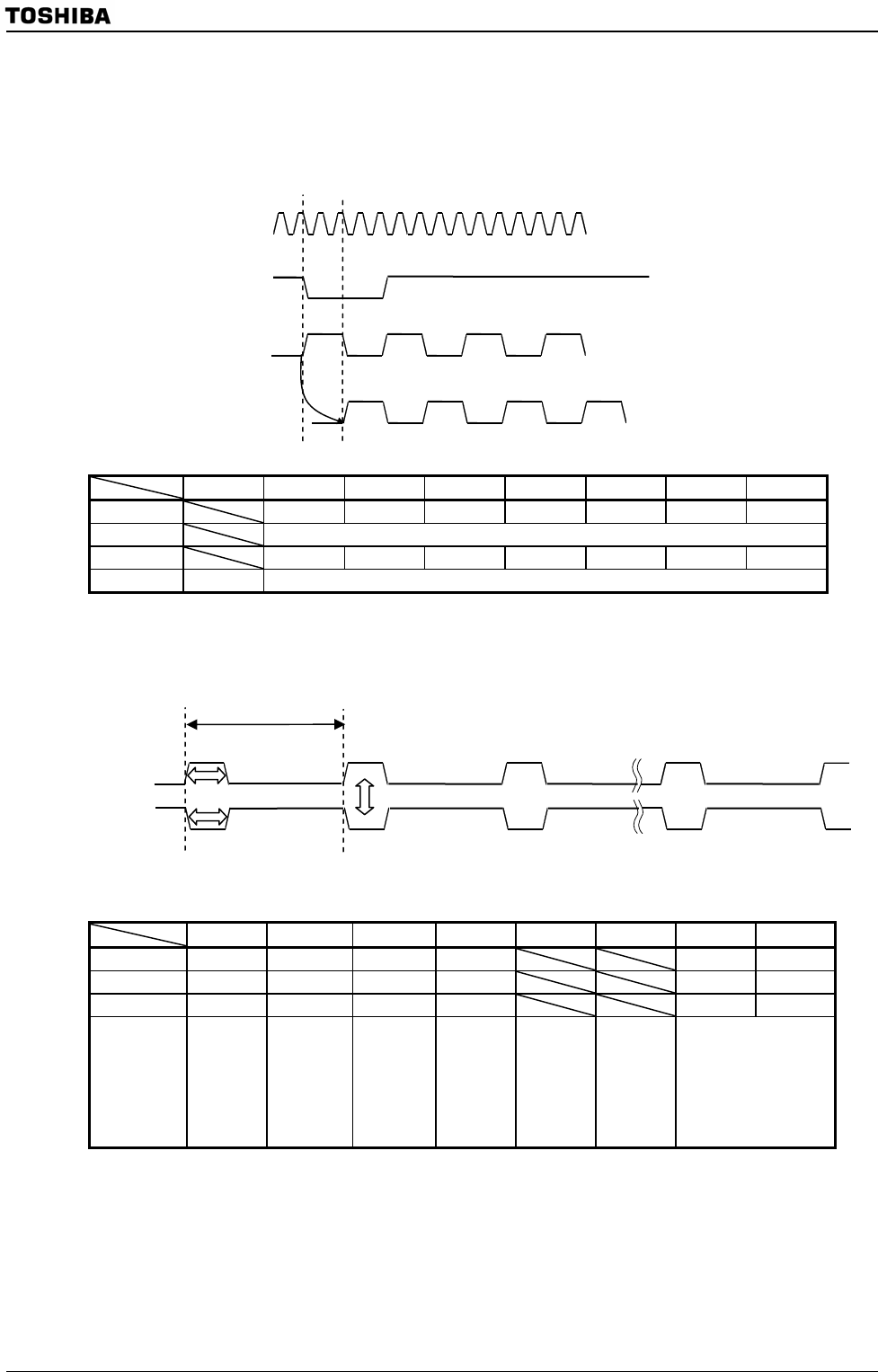

As shown in the diagram below, delay time of 0 to 127 pulses of the LCP0 clock can be

inserted in the LHSYNC signal.

Delay time = <HSD6:0>

LCDHSDLY Register

7 6 5 4 3 2 1 0

bit Symbol HSD6 HSD5 HSD4 HSD3 HSD2 HSD1 HSD0

Read/Write W

After reset 0 0 0 0 0 0 0

Function LHSYNC delay (bits 6-0)

The phase of the LHSYNC signal can be inverted by the setting of LCDCTL1

<LVSP>.

LCD Control 1 Register

7 6 5 4 3 2 1 0

bit Symbol LCP0P LHSP LVSP LLDP LVSW1 LVSW0

Read/Write R/W R/W R/W R/W R/W R/W

After reset 1 0 1 0 0 0

Function

LCP0

phase

0: Rising

1: Falling

LHSYNC

phase

0: Rising

1: Falling

LVSYNC

phase

0: Rising

1: Falling

LLOAD

phase

0: Rising

1: Falling

LVSYNC

enable time control

00 : 1 clock of LHSYNC

01 : 2 clocks of LHSYNC

10 : 3 clocks of LHSYNC

11 : Reserved

LCP0 signal

Signal Name

LVSYNC signal

Reference LHSYNC

(with 0 delay)

LHSYNC signal

Delay control 1

(Phase control)

(Enable width control)

LHSP=0

LHSP=1

LHSYNC period

LHSYNC signal

LCDHSDLY

(028FH)

LCDCTL1

(

0286H

)