TMP92CZ26A

92CZ26A-115

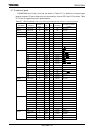

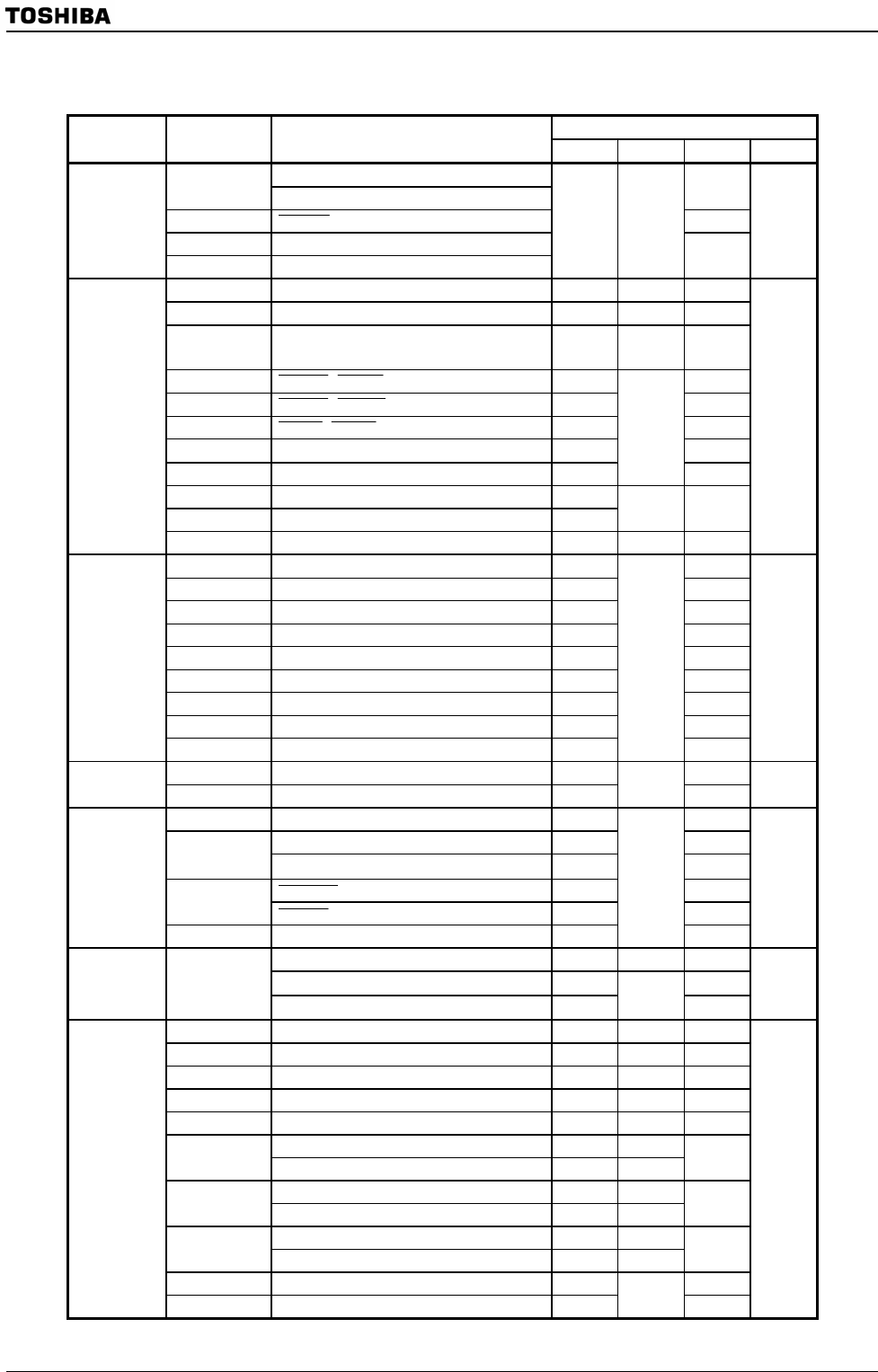

Table3.7.2 I/O Port and Specifications (3/4)

X: Don’t care

I/O register

Port Pin name Specification

Pn PnCR PnFC PnFC2

Input port PG0 to PG5

AN0 to AN5 Input

0

PG3

ADTRG

Input

1

PG2 MX Output Note:

Port G

PG3 MY Output Note:

X None

0

None

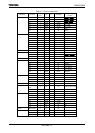

PJ5 to PJ6 Input port X 0 0

PJ5 to PJ6 Output port X 1 0

PJ0 to PJ4,

PJ7

Output port X None 0

PJ0

SDRAS

,

SRLLB

Output

X 1

PJ1

SDCAS

,

SRLUB

Output

X 1

PJ2

SDWE

,

SRWR

Output

X 1

PJ3 SDLLDQM Output

X 1

PJ4 SDLUDQM Output X

None

1

PJ5 NDALE Output X

PJ6 NDCLE Output X

1 1

Port J

PJ7 SDCKE Output X None 1

None

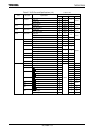

PK0 to PK7 Output port X 0

PK0 LCP0 output X 1

PK1 LLOAD output X 1

PK2 LFR output X 1

PK3 LVSYNC output X 1

PK4 LHSYNC output X 1

PK5 LGOE0 output X 1

PK6 LGOE1 output X 1

Port K

PK7 LGOE2 output X

None

1

None

PL0 to PL7 Output port X 0 Port L

PL0 to PL7 LD0 to LD7 Output X

None

1

None

PM1 to PM2 Output port

X 0

TA1OUTOutput 0 1 PM1

MLDALM Output

1 1

MLDALM

Output

0 1

PM2

ALARM

Output

1 1

Port M

PM7 PWE Output X

None

1

None

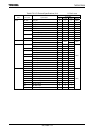

Input port X 0 0

Output port (CMOS Output) X 0

Port N PN0 to PN7

KO Output (Open-drain Output) X

1

1

None

PP1 to PP5 Input port X 0 0

PP1 to PP5 Output port X 1 0

PP6 to PP7 Output port X None 0

PP1 TA3OUT output X 1 1

PP2 TA5OUT output X 1 1

INT5 input X 0 PP3

TA7OUT output X 1

1

INT6 input X 0 PP4

TB0IN0 input X 1

1

INT7 input X 0 PP5

TB1IN0 input X 1

1

PP6 TB0OUT0 output X 1

Port P

PP7 TB1OUT1 output X

None

1

None

Note: Case of using touch screen