TMP92CZ26A

92CZ26A-116

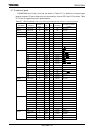

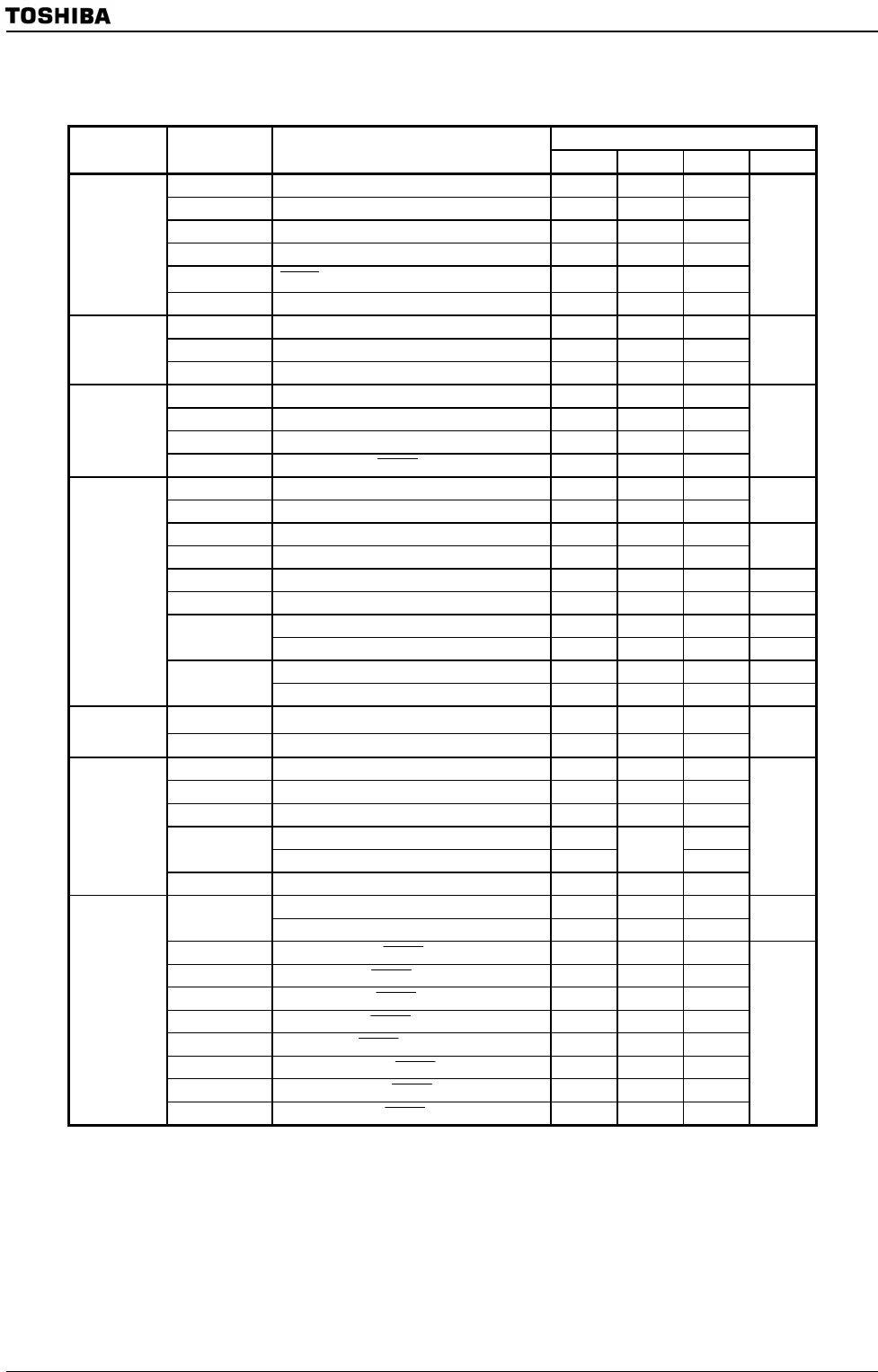

Table 3.7.2 I/O Port and Specifications (4/4)

X: Don’t care

I/O register

Port Pin name Specification

Pn PnCR PnFC PnFC2

PR0 to PR3 Input port X 0 0

PR0 to PR3 Output port X 1 0

PR0 SPDI Input X 0 1

PR1 SPDO Output X 1 1

PR2

SPCS Output

X 1 1

Port R

PR3 SPCLK Output X 1 1

None

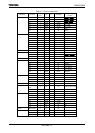

PT0 to PT7 Input port X 0 0

PT0 toPT7 Output port X 1 0

Port T

PT0 to PT7 LD8 to LD15 Output X 1 1

None

PU0 to PU7 Input port X 0 0

PU0 to PU7 Output port X 1 0

PU0 to PU7 LD16 to LD23 Output X 1 1

Port U

PU7

EO_TRGOUT (

DBGE

= “0”) Note:

X X X

None

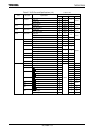

PV0 to PV2 Input port X 0 0

PV0 to PV4 Output port X 1 0

None

PV6 to PV7 Input port X 0 0

PV6 to PV7 Output port X 1 0

0

PV6 to PV7 Output port (Open-drain) X 1 0 1

PV0 SCLK0 Output X 1 1 None

SDA I/O X 1 1 0 PV6

SDA I/O (Open-drain) X 1 1 1

SCL I/O X 1 1 0

Port V

PV7

SCL I/O (Open-drain) X 1 1 1

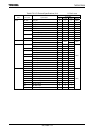

PW0 to PW7 Input port

X 0 0

Port W

PW0 to PW7 Output port X 1 0

None

PX5, PX7 Input port X 0 0

PX4 Output port X None 0

PX5, PX7 Output port X 1 0

CLKOUT Output 0 1 PX4

LDIV Output 1

None

1

Port X

PX5 X1USB Input X 0 1

None

Input port X 0 0 PZ0 to PZ7

Output port X 1 0

None

PZ0

EI_PODDATA (

DBGE

= “0”) Note:

X X X

PZ1

EI_SYNCLK (

DBGE

= “0”) Note:

X X X

PZ2

EI_PODREQ (

DBGE

= “0”) Note:

X X X

PZ3

EI_REFCLK (

DBGE

= “0”) Note:

X X X

PZ4

EI_TRGIN (

DBGE

= “0”) Note:

X X X

PZ5

EI_COMRESET (

DBGE

= “0”) Note:

X X X

PZ6

EO_MCUDATA (

DBGE

= “0”) Note:

X X X

Port Z

PZ7

EO_MCUREQ (

DBGE

= “0”) Note:

X X X

None

Note: When Debug mode, it is set to the Debug pin regardless of port setting.