TMP92CZ26A

92CZ26A-490

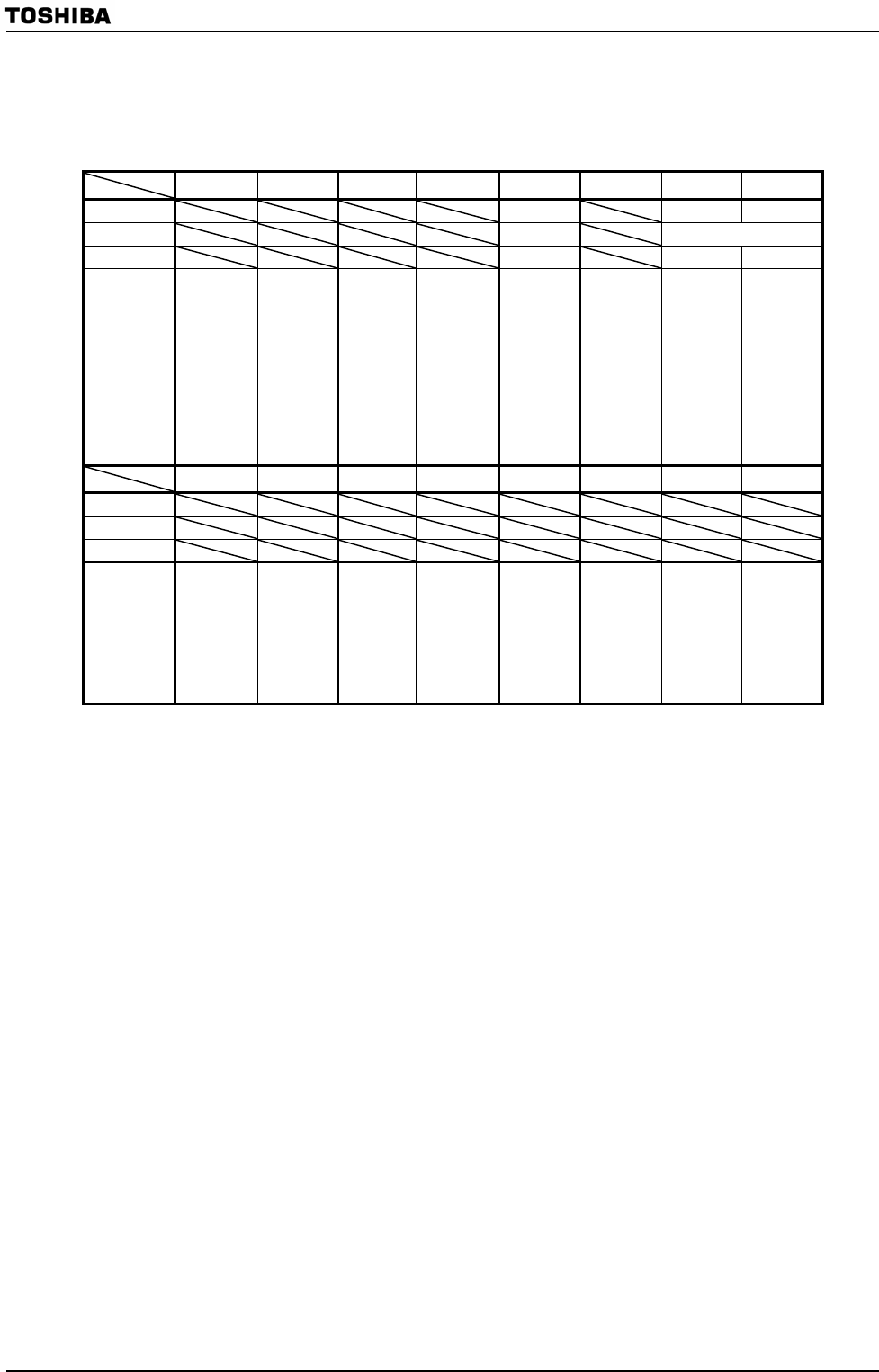

(3-1) SPIST (SPI Status Register)

SPIST shows 4 statuses.

SPIST Register

7 6 5 4 3 2 1 0

bit Symbol

TEMP TEND REND

Read/Write

R R

After reset

1 1 0

Function

Transmit FIFO

Status

0: no space

1: having

space

Transmit

Status

0: during

transmission

or having

transmission

data

1: finish

Receive

Status

0: during

receiving

or not having

receiving

data

1: finish or not

having space

15 14 13 12 11 10 9 8

bit Symbol

Read/Write

After reset

Function

Figure 3.17.9 SPIST Register

(a) <TEMP>

For UNIT transmission, it is cleared to “0” when valid data exists in transmit register

(SPITD). It is set to “1” when no valid data exists.

For Sequential transmission, it is set to “1” when no valid data exists in transmit buffer.

(b) <TEND>

This bit is cleared to “0” when valid data to transmit exists in the shift register/FIFO buffer

or when transmission. It is set to “1” when no valid data exists in the transmit data

register/FIFO buffer and finish transmitting all the data.

(c) <REND>

For UNIT receiving, it is set to “1” when finish receiving and valid data was loaded to

receive data register (when valid data exists). It is cleared to “0” when no valid data exists

in receive register (SPIRD). It is set to “1” when no valid data exists or during receiving.

For Sequential receiving, it is set to “1” when valid data of 32 bytes exist in receive FIFO

after finish receiving last data. It is cleared to “0” even if having space of 1byte.

RFUL flag does not exist because meaning is the same with REND flag.

SPIST

(824H)

(825H)