TMP92CZ26A

92CZ26A-118

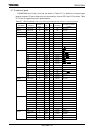

Port 1 register

7 6 5 4 3 2 1 0

bit Symbol P17 P16 P15 P14 P13 P12 P11 P10

Read/Write R/W

After reset Data from external port (Output latch register is cleared to “0”)

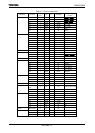

Port 1 Control register

7 6 5 4 3 2 1 0

bit Symbol P17C P16C P15C P14C P13C P12C P11C P10C

Read/Write W

After reset 0 0 0 0 0 0 0 0

Function 0: Input 1: Output

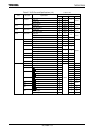

Port 1 Function register

7 6 5 4 3 2 1 0

bit Symbol P1F

Read/Write W

After reset

Note2:

0/1

Function

0: Port

1:Data bus

(D8 to D15)

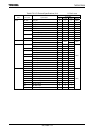

Port 1 Drive register

7 6 5 4 3 2 1 0

bit Symbol P17D P16D P15D P14D P13D P12D P11D P10D

Read/Write

R/W

After reset 1 1 1 1 1 1 1 1

Function Input/Output buffer drive register for standby mode

Note1: Read-modify-write is prohibited for P1CR, P1FC.

Note2: It is set to “Port” or “Data bus” by AM pins state.

Figure 3.7.2 Register for Port1

P1

(0004H)

P1FC

(0007H)

P1CR

(0006H)

P1DR

(0081H)