TMP92CZ26A

92CZ26A-443

(a) Single packet mode

This is data sequence of single packet mode when CPU bus interface is used.

Figure 3.16.15 is receiving sequence. Figure 3.16.16 is transmitting sequence.

Main of this chapter is access to FIFO. Data sequence with USB host refer to

chapter 5.

Endpoint 0 can’t be changed mode for exclusive single packet mode. Single

packet and dual packet of endpoint 1 to 3 can change by setting Epx_SINGLE

register. When transferring, don’t change packet.

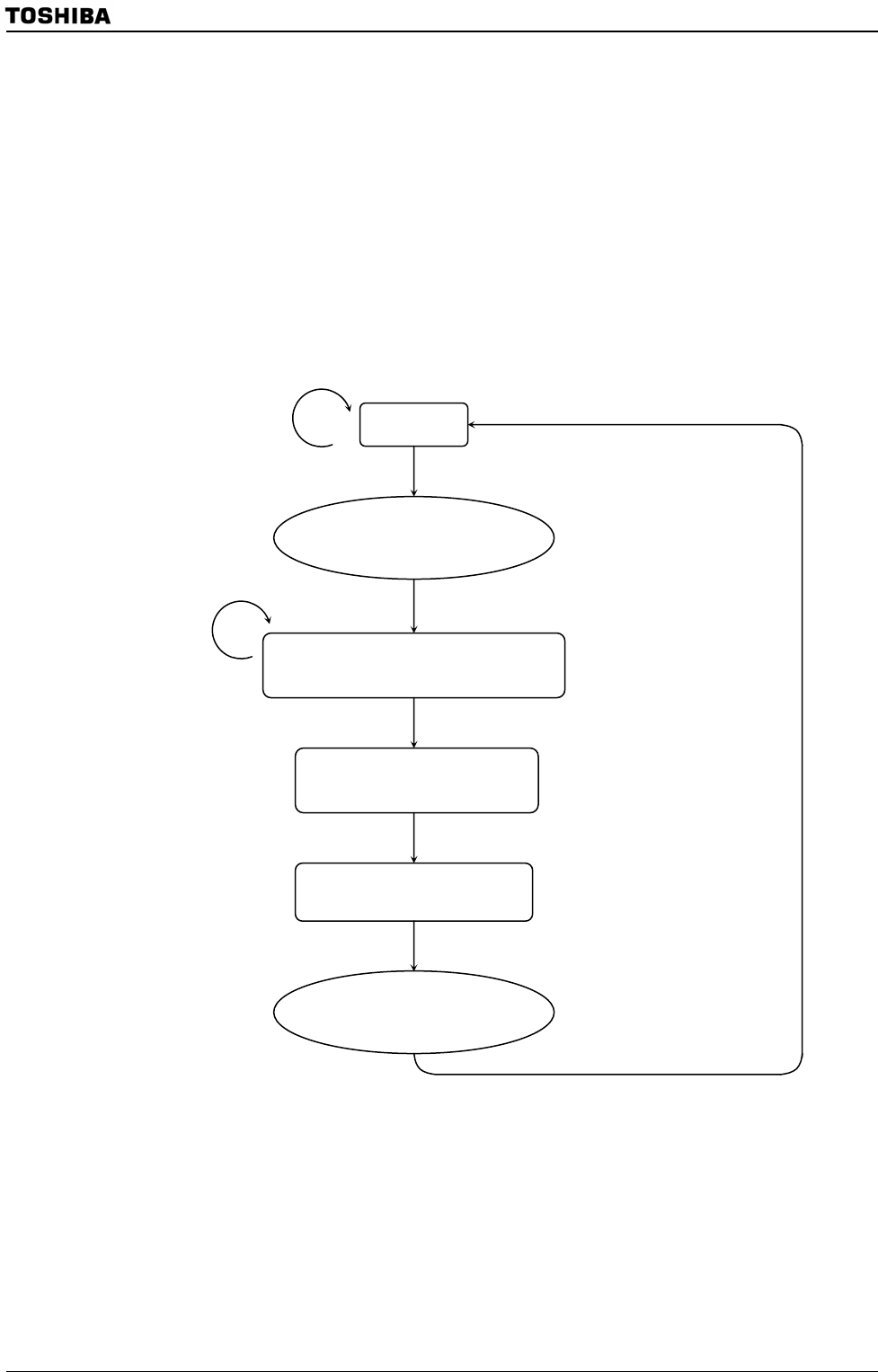

Figure 3.16.15 Receiving Sequence in Single Packet Mode

IDLE

DATASET register

• Check bit of EPx_DSET_A

SIZE register

• Size of SIZE_A_L confirmation

• Size of SIZE_A_H confirmation

RD receiving data of size in

appricable endpoint

DATASET = 1

DATASET register

• Set bit of EPx_D SET_A

• Assert EPx_DATASET signal

• Clear receiving data in FIFO

• Clear applicable bit of DATASET

register

Interrupt by EPx_FULLA

Check DATASET register

Receive valid data

DATASET = 0

Wait receiving data