TMP92CZ26A

92CZ26A-95

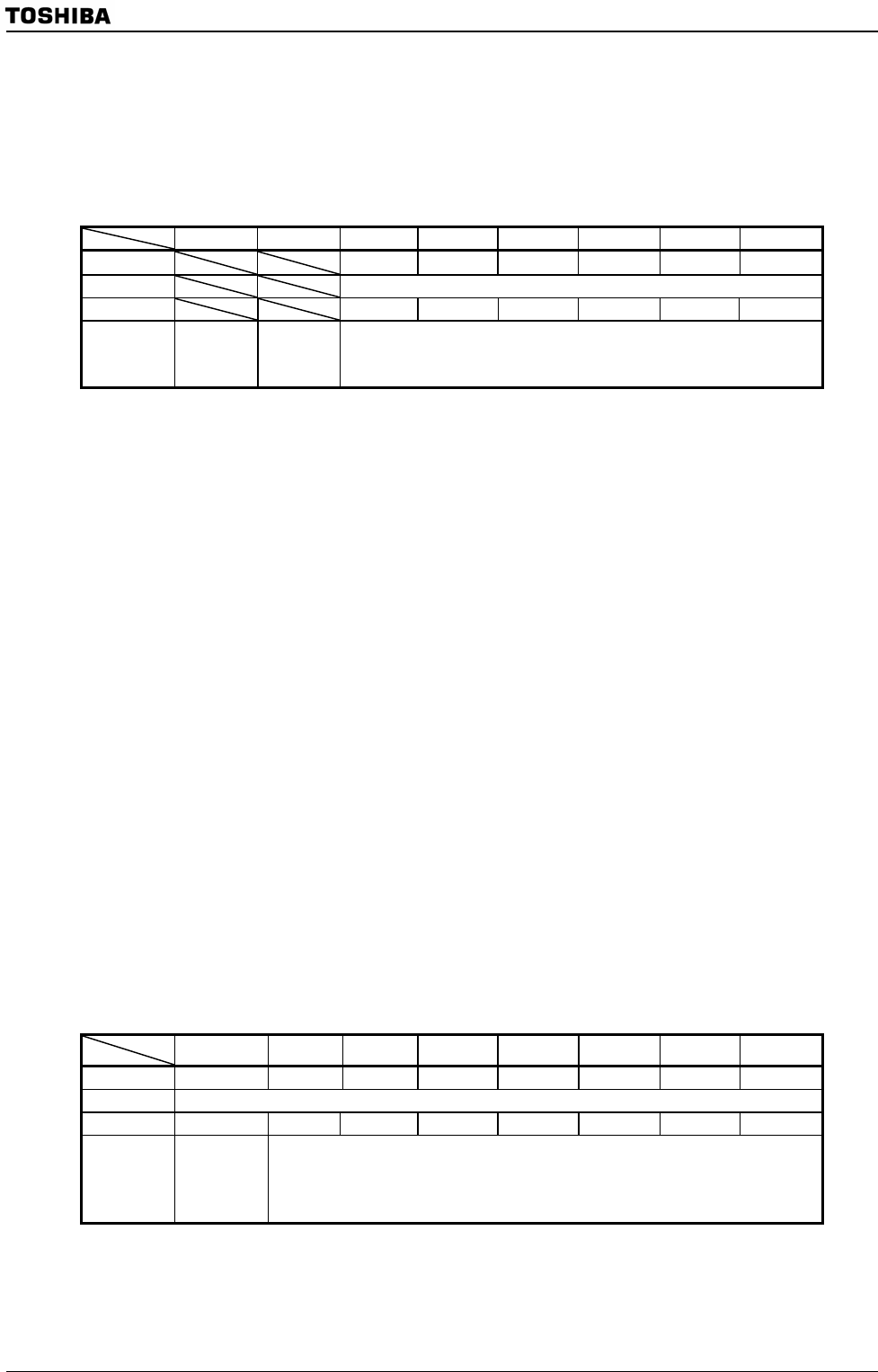

(6) HDMAE (DMA Operation Enable Register)

The HDMAE register is used to enable or disable the DMAC operation.

Bits 0 to 5 correspond to channels 0 to 5. Unused channels should be set to “0”.

HDMAE Register

7 6 5 4 3 2 1 0

bit Symbol DMAE5 DMAE4 DMAE3 DMAE2 DMAE1 DMAE0

Read/Write R/W

After reset 0 0 0 0 0 0

Function

DMA channel operation

0: Disable

1: Enable

Note: Read-modify-write instructions can be used on this register.

Figure 3.6.7 HDMAE Register

(7) HDMATR (DMA Maximum Bus Occupancy Time Setting Register)

The HDMATR register is used to set the maximum duration of time the DMAC can

occupy the bus. The TMP92CZ26A does not have priority levels for bus arbitration.

Therefore, once the DMAC owns the bus, other masters (such as the LCDC) must wait until

the DMAC completes its transfer operation and releases the bus. This could lead to

problems in the system. For example, if the LCDC cannot own the bus as required, the LCD

display function may not work properly. To avoid such a situation, the DMAC limits the

duration of its bus occupancy by using this timer register. When the DMAC occupies the

bus for the duration of time set in this register, it releases the bus even if the specified DMA

operation has not been completed yet. After waiting for 16 states, the DMAC asserts a bus

request again to execute the rest of the DMA operation.

The DMAC counts the bus occupancy time regardless of which channel is occupying the

bus. To set the maximum bus occupancy time, ensure that the HDMAE register is set to

“00H” and set HDMATR<DMATE> to “1” and <DMATR6:0> to the desired value.

Note: In case of using S/W start with HDMA, transmission start is to set to "1" DMAR

register. However DMAR register can't be used to confirm flag of transmission end. DMAR

register reset to "0" when HDMA release bus occupation once with HDMATR function.

HDMATR Register

7 6 5 4 3 2 1 0

bit Symbol DMATE DMATR6 DMATR5 DMATR4 DMATR3 DMATR2 DMATR1 DMATR0

Read/Write R/W

After reset 0 0 0 0 0 0 0 0

Function

Timer

operation

0: Disable

1: Enable

Maximum bus occupancy time setting

The value to be set in <DMATR6:0> should be obtained by

“maximum bus occupancy time / (256/f

SYS

)”.

“00H” cannot be set.

Note: Read-modify-write instructions can be used on this register.

Figure 3.6.8 HDMATR Register

HDMAE

(097EH)

HDMATR

(097FH)