TMP92CZ26A

92CZ26A-396

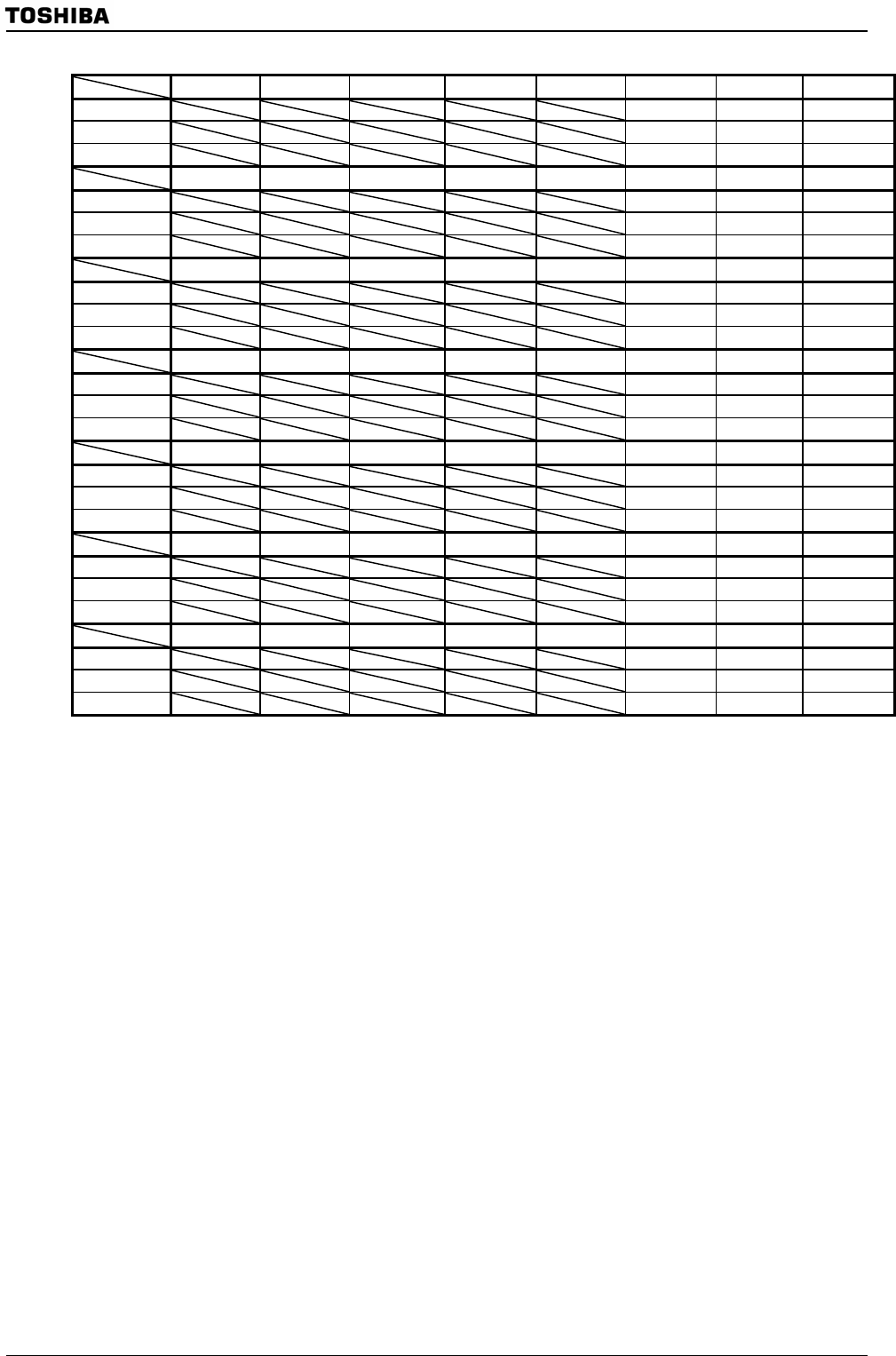

7 6 5 4 3 2 1 0

bit Symbol DATASIZE9 DATASIZE8 DATASIZE7

Read/Write R R R

After reset 0 0 0

7 6 5 4 3 2 1 0

bit Symbol DATASIZE9 DATASIZE8 DATASIZE7

Read/Write R R R

After reset 0 0 0

7 6 5 4 3 2 1 0

bit Symbol DATASIZE9 DATASIZE8 DATASIZE7

Read/Write R R R

After reset 0 0 0

7 6 5 4 3 2 1 0

bit Symbol DATASIZE9 DATASIZE8 DATASIZE7

Read/Write R R R

After reset 0 0 0

7 6 5 4 3 2 1 0

bit Symbol DATASIZE9 DATASIZE8 DATASIZE7

Read/Write R R R

After reset 0 0 0

7 6 5 4 3 2 1 0

bit Symbol DATASIZE9 DATASIZE8 DATASIZE7

Read/Write R R R

After reset 0 0 0

7 6 5 4 3 2 1 0

bit Symbol DATASIZE9 DATASIZE8 DATASIZE7

Read/Write R R R

After reset 0 0 0

Note EP3,4,5,6,7_SIZE_H_B registers are not used at TMP92CZ26A.

DATASIZE[9:7] (H register: Bit2 to bit0)

DATASIZE[6:0] (L register: Bit6 to bit0) In receiving, data number that 1 packet received

from the host is shown. This is renewed when a data

from the host is received with no error.

PKT_ACTIVE (L register: Bit7)

1: OUT_ENABLE

0: OUT_DISABLE

When dual-packet mode is selected, this bit show

packet that can be accessed. In this case, the UDC

accesses packets that divide FIFO (Packet A and

Packet B) mutually. When FIFO in UDC is accessed by

CPU, refer to this bit. If receiving endpoint, start

reading from packet that this bit is “1”.

In single-packet

mode, this bit is no meaning because of the packet-

A

is

always used.

EP1_SIZE_H_B

(07B1H)

EP2_SIZE_H_B

(07B2H)

EP3_SIZE_H_B

(07B3H)

EP4_SIZE_H_B

(07B4H)

EP5_SIZE_H_B

(07B5H)

EP6_SIZE_H_B

(07B6H)

EP7

_

SIZE_H_B

(07B7H)