TMP92CZ26A

92CZ26A-552

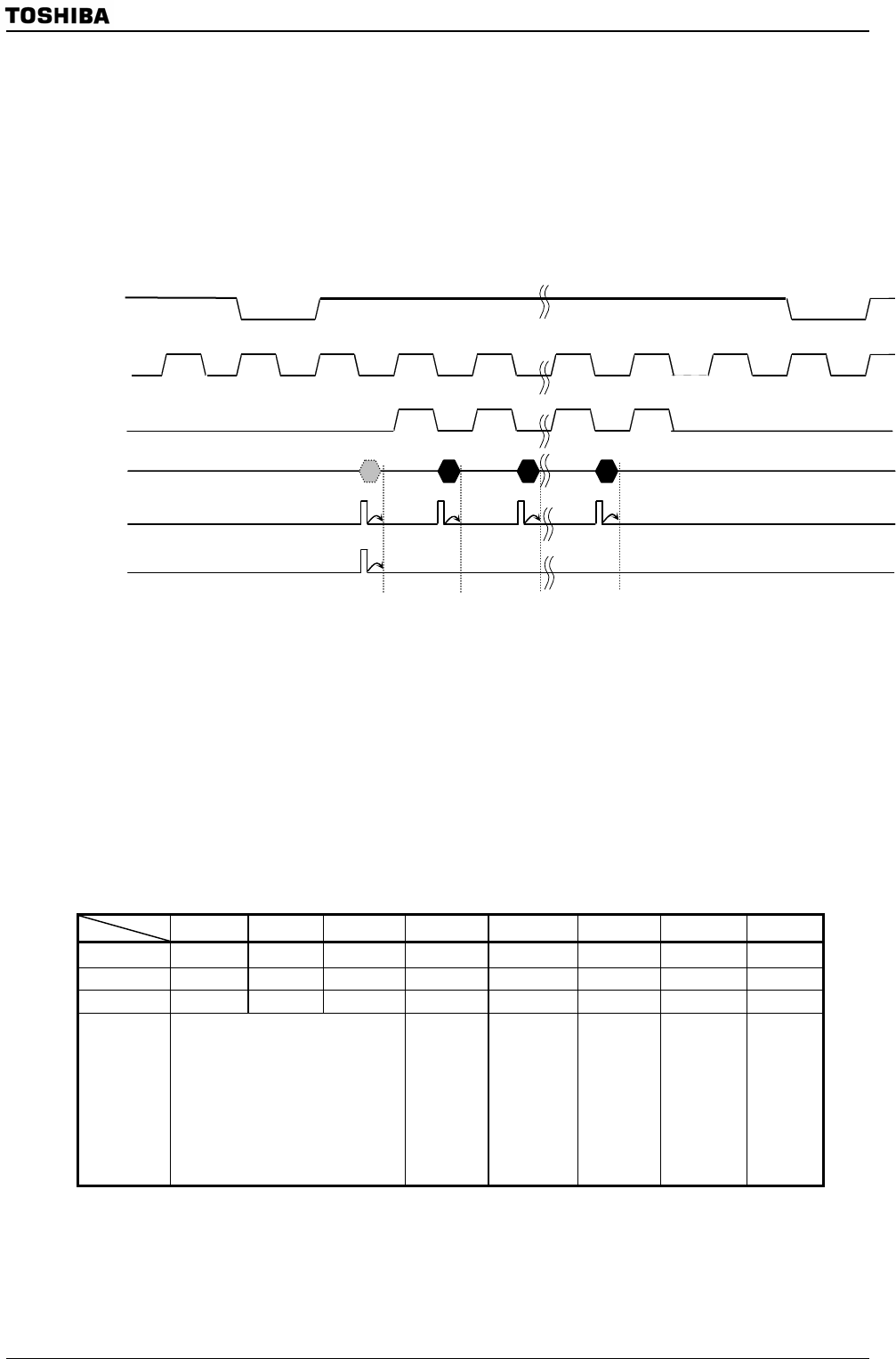

3.19.4 Interrupt Function

The LCDC has two types of interrupts.

One is generated synchronous with the LLOAD signal and the other is generated

synchronous with the LLOAD signal that is output immediately after the LVSYNC

signal.

LCDMODE1<INTMODE> is used to switch between these two types of interrupts.

When LCDMODE1<INTMODE>=0, an interrupt request is generated at the start of

each VRAM read before the LLOAD generates (once in each LLOAD period).

When LCDMODE1<INTMODE>=1, an interrupt request is generated at the start of

VRAM read before the first LLOAD generates (once in each LVSYNC period).

**The interrupt request generates when reading the data from VRAM at once. Since

reading from VRAM is executed by DMA with bus request to the CPU, DMA operation

is given priority. Thus CPU accepts interrupt immediately after reading the data from

VRAM.

LCDMODE1 Register

7 6 5 4 3 2 1 0

bit Symbol LDC2 LDC1 LDC0 LDINV AUTOINV INTMODE FREDGE SCPW2

Read/Write R/W R/W R/W R/W R/W R/W W W

After reset 0 0 0 0 0 0 0 0

Function

Data rotation function

(Supported for 64K-color: 16 bps

only)

000: Normal 100: 90-degree

001: Horizontal flip 101: Reserved

010: Vertical flip 110: Reserved

011: Vertical & 111: Reserved

horizontal flip

LD bus

inversion

0: Normal

1: Invert

Auto bus

inversion

0: Disable

1: Enable

(Valid only

for TFT)

Interrupt

selection

0:LLOAD

1:LVSYNC

LFR edge

0: LHSYNC

Front Edge

1:LHSYNC

Rear Edge

LD bus

Trance

Speed

0: normal

1: 1/3

Note: The LCDMODE1<INTMODE> setting must not be changed while the LCDC is operating. Be sure to set

LCDCTL0<START> to “0” to stop the LCDC operation before changing the interrupt setting.

LVSYNC

LHSYNC

LLOAD

D15-0(VRAM Read)

Interrupt request

LCDMODE1<INTMODE>=0

Interrupt request

LCDMODE1<INTMODE>=1

LCDMODE1

(

0281H

)