TMP92CZ26A

92CZ26A-433

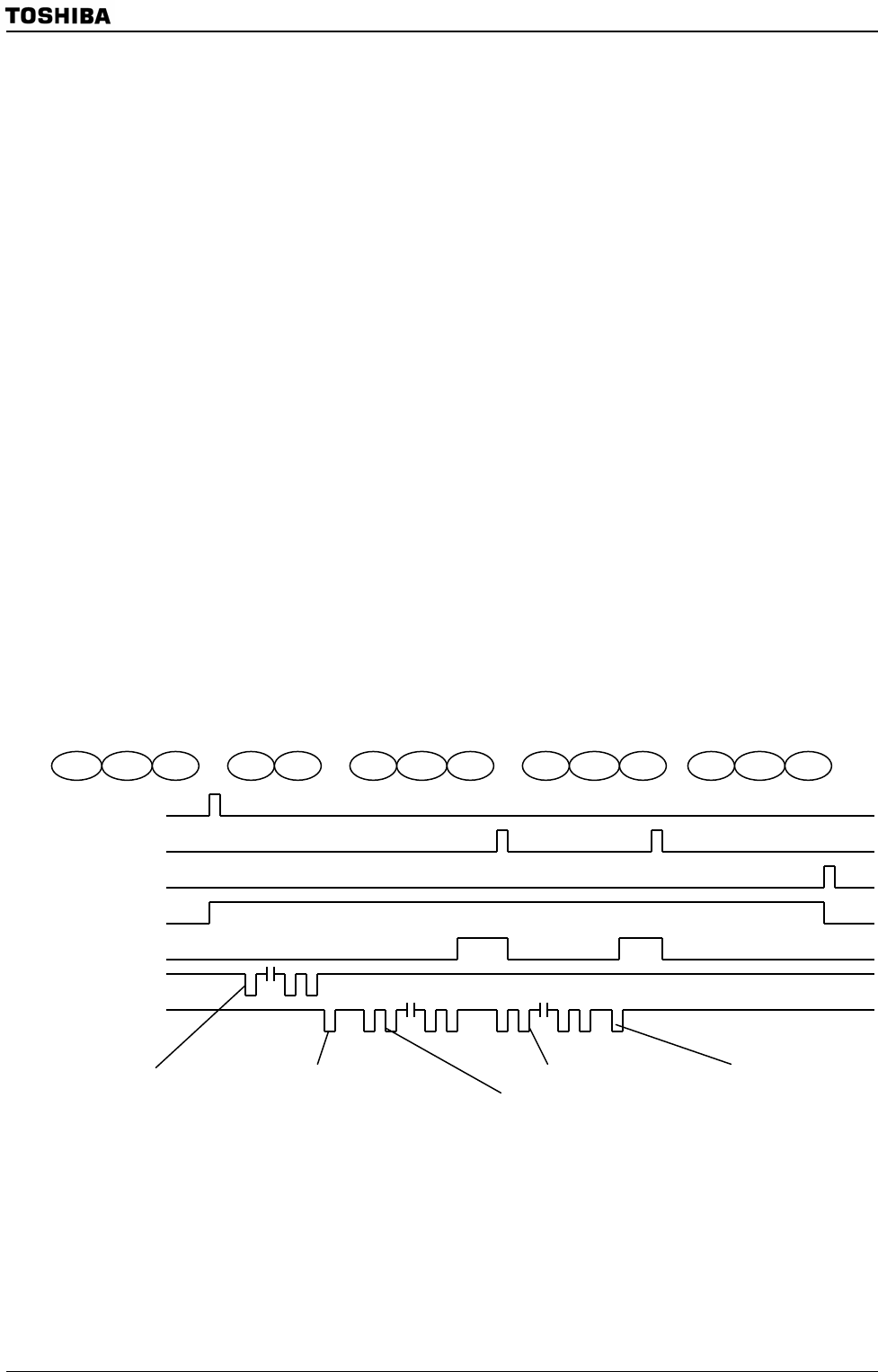

Stage change condition of control read transfer type

1. Receive SETUP token from host

• Start setup stage in UDC.

• Receive data in request normally and judge. And assert INT_SETUP

interrupt to external.

• Change data stage into the UDC.

2. Receive IN token from host

• CPU receive request from request register every INT_SETUP

interrupt.

• Judge request and access Setup Received register for inform that

recognized INT_SETUP interrupt to UDC.

• According to Device request, monitor EP0 bit of DATASET register,

and write data to FIFO.

• If UDC is set data of payload to FIFO or CPU set short packet

transfer in EOP register, EP0 bit of DATASET register is set.

• UDC transfers data that is set to FIFO to host by IN token interrupts.

• When CPU finish transaction, it writes “0” to EP0 bit of EOP register.

• Change status stage in UDC.

3. Receive OUT token from host.

• Return ACK to OUT token, and state change to IDLE in UDC.

• Assert INT_STATUS interrupt to external.

These changing conditions are shown in

Figure 3.16.10.

Figure 3.16.10 The Control Flow in UDC (Control Read Transfer Type)

SETUP DATA0 ACK IN NAK DATA1 DATA0 DATA1

INT_SETUP

INT_ ENDPOINT0

INT_STATUS

REQUEST FLAG

DATASET register

BRD

BWR

bmRequestType registe

r

bRequest register

wValue register

wIndex register

wLength register

Setup Received registe

r

EP0_FIFO (WR of payload)

EP0_FIFO (Rest data) EOP registe

r

IN ACK IN ACK OUT ACK