TMP92CZ26A

92CZ26A-418

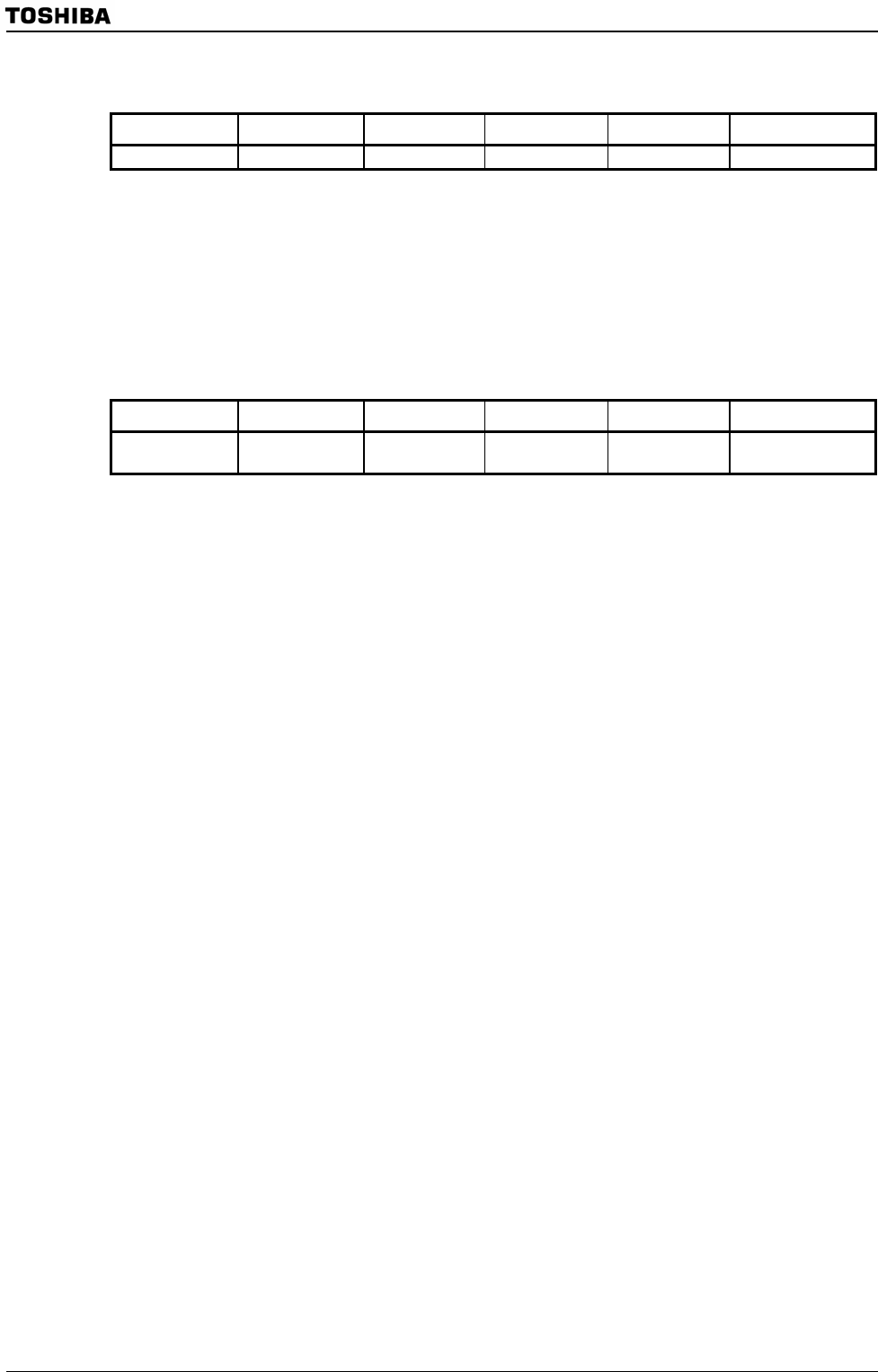

(b) Control write/request

There is no dataphase

bmRequestType bRequest wValue wIndex wLength Data

010000xxB Vendor peculiar Vendor peculiar Vendor peculiar 0 None

When INT_SETUP is received, judge contents of receiving request by

bmRequestType, bRequest, wValue, wIndex, wLength registers. And execute

transaction for each request. As application, access Setup_Received register

after request was judged. And it must inform that INT_SETUP interrupt was

recognized to UDC. If transaction of application finished, write “0” to EP0 bit

of EOP register. When UDC receive it, status stage finish automatically.

There is dataphase

bmRequestType bRequest wValue wIndex wLength Data

010000xxB Vendor peculiar Vendor peculiar Vendor peculiar Vendor peculiar

(Except for 0)

Vendor data

When INT_SETUP is received, judge contents of receiving device request

by bmRequestType, bRequest, wValue, wIndex, wLength registers. And

execute transaction for each request. As application, access Setup_Received

register after request was judged. And it must inform that INT_SETUP

interrupt was recognized to UDC.

After receiving data prepared in application, access DATASET register, and

confirm EP0_DSET is “1”. After confirming, read data FIFO of endpoint 0. If

receiving data more than payload, write data after it confirmed whether a bit

of EP0_DSET_A in DATASET register is “1”. (INT_ENDPOINT0 interrupt is

can be used.) If reading all data finish, write “0” to EP0 bit of EOP register.

When UDC receive it, status stage finished automatically.

And when UDC finish status stage normally, INT_STATUS interrupt is

asserted. If finishing status stage normally is recognized to external

application, manage this stage by using this interrupt signal. If status stage

cannot be finished normally and during status stage, maybe new SETUP

token is received. In this case, when INT_SETUP interrupt signal is asserted,

“1” is set to STAGE_ERROR bit of EP0_STATUS register. And it informs it to

external that status stage cannot be finished normally.