TMP92CZ26A

92CZ26A-329

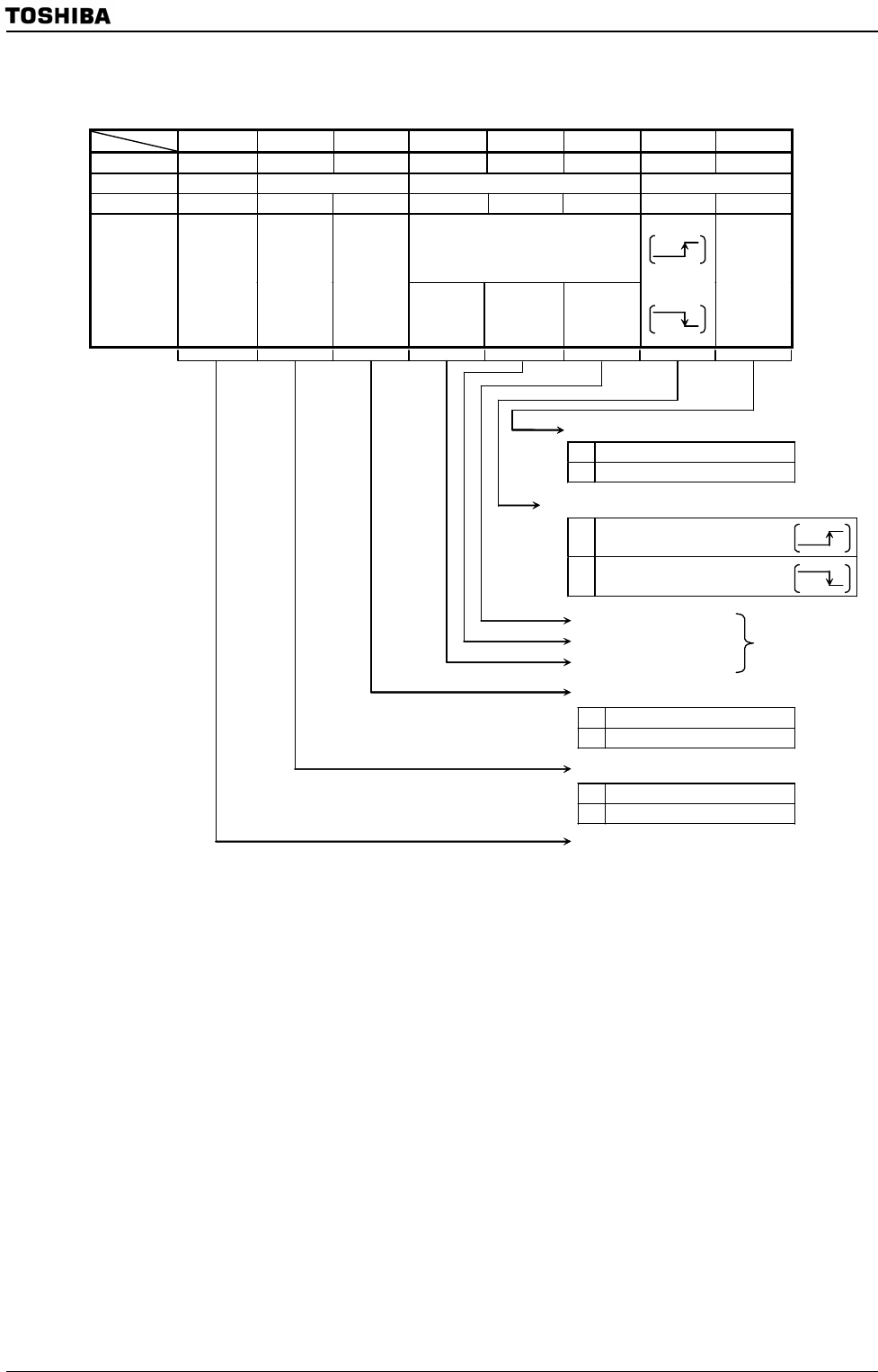

7 6 5 4 3 2 1 0

bit Symbol RB8 EVEN PE OERR PERR FERR SCLKS IOC

Read/Write R R/W R (cleared to 0 when read) R/W

After Reset Undefined 0 0 0 0 0 0 0

Function

Received

data bit 8

Parity

0: odd

1: even

Parity

addition

0: disable

1: enable

Overrun Parity Framing

0: SCLK0

1: SCLK0

0: baud rate

generator

1: SCLK0

pin input

SC0CR

(1201H)

I/O interface input clock selection

Framing Error flag

Parity Error flag

Overrun Error flag

0

Transmits and receivers

data on rising edge of SCLK0.

1

Transmits and receivers

data on falling edge SCLK0.

Edge selection for SCLK pin (Input / Output Mode)

0 Disabled

1 Enabled

Parity addition enables

Even parity addition/check

1: error

0 Baud rate generator

1 SCLK0 pin input

Cleared to 0

when read

0 Odd parity

1 Even parity

Received data 8

Prohibit

to Read

modify

Write

Note: As all error flags are cleared after reading, do not test only a single bit with a bit-testing

instruction.

Figure 3.14.7 Serial Control Register (channel 0, SC0CR)