TMP92CZ26A

92CZ26A-188

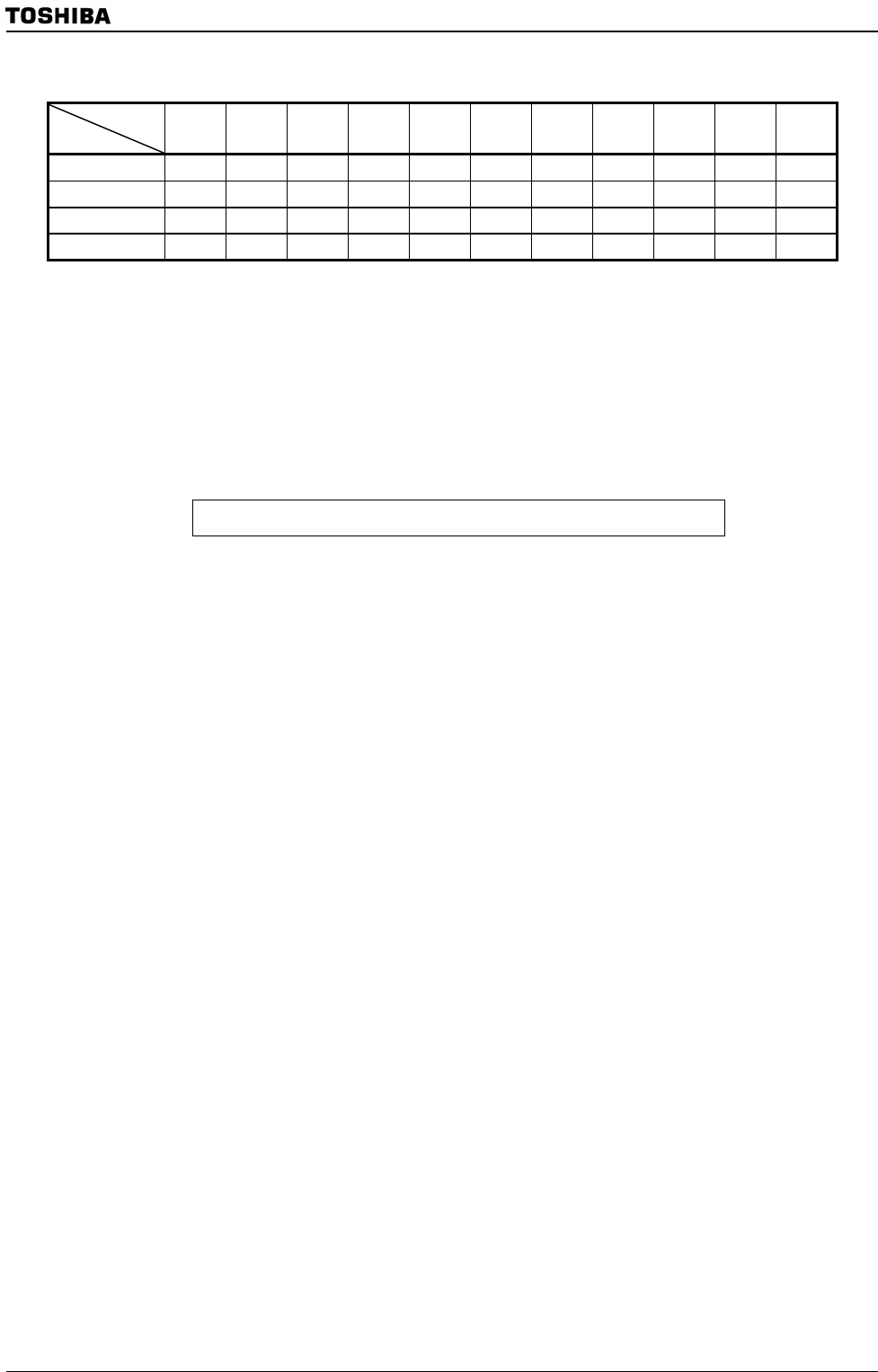

Table 3.8.3 Valid Area Sizes for Each CS Area

Size

(Byte)

CS area

256 512 32 K 64 K 128 K 256 K 512 K 1 M 2 M 4 M 8 M

CS0

○ ○ ○ ○

Δ Δ Δ Δ Δ

CS1

○ ○

○

Δ Δ Δ Δ Δ Δ

CS2

○ ○

Δ Δ Δ Δ Δ Δ Δ

CS3

○ ○

Δ Δ Δ Δ Δ Δ Δ

Note:“Δ” indicates areas that cannot be set by memory start address register and address mask

register combinations.

(e) Block address area Priority

When the set block address area overlaps with the built-in memory area, or both two

address areas overlap, the block address area is processed according to priority as follows.

(f) Wait control for outside the block address area of CS0 to CS3

Also, that any accessed areas outside the address spaces set by CS0 to CS3 are processed

as the CSEX space. Therefore, settings of CSEX (BEXCSH, L-register) apply for the control

of wait cycles, data bus width, etc,.

Built-in I/O > Built-in memory > Block address area 0 > 1 > 2 > 3