TMP92CZ26A

92CZ26A-38

(3) Operation

a. IDLE2 Mode

In IDLE2 Mode, only specific internal I/O operations, as designated by the

IDLE2 Setting Register, can take place. Instruction execution by the CPU stops.

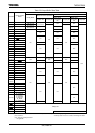

Figure 3.3.8 illustrates an example of the timing for clearance of the IDLE2

Mode Halt state by an interrupt.

Figure 3.3.8 Timing chart for IDLE2 Mode Halt state cleared by interrupt

b. IDLE1 Mode

In IDLE1 Mode, only the internal oscillator and the RTC and MLD continue to

operate. The system clock stops.

In the Halt state, the interrupt request is sampled asynchronously with the

system clock; however, clearance of the Halt state (i.e. restart of operation) is

synchronous with it.

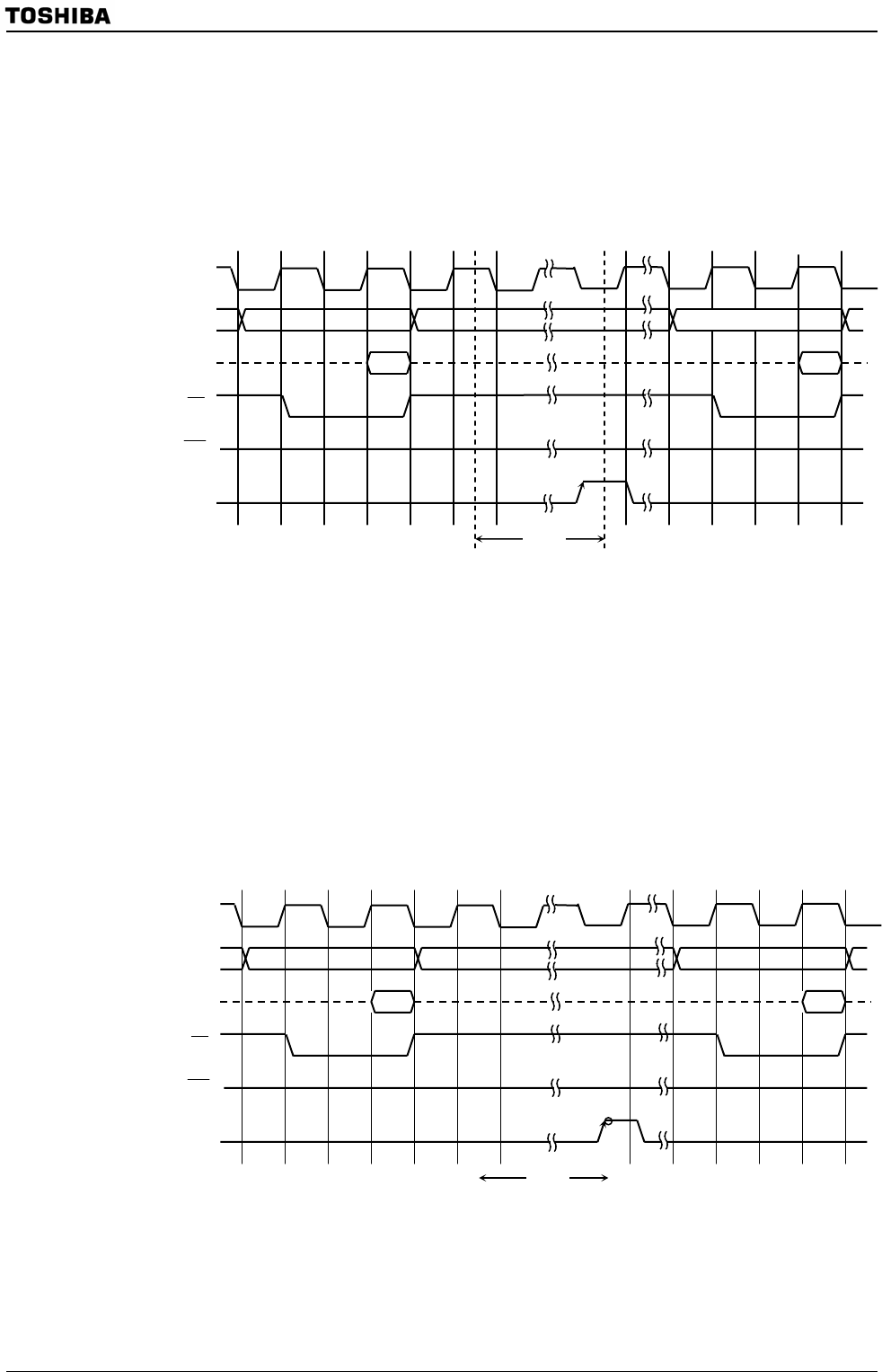

Figure 3.3.9 illustrates the timing for clearance of the IDLE1 Mode Halt state by

an interrupt.

Figure 3.3.9 Timing chart for IDLE1 Mode Halt state cleared by interrupt

IDLE2

mode

Data

X1

A0~A23

D0~D31

RD

WR

Data

Interrupt fo

r

releasing Halt

IDLE1

mode

Data Data

X1

A0~A23

D0~D31

RD

WR

Interrupt fo

r

releasing Halt