TMP92CZ26A

92CZ26A-539

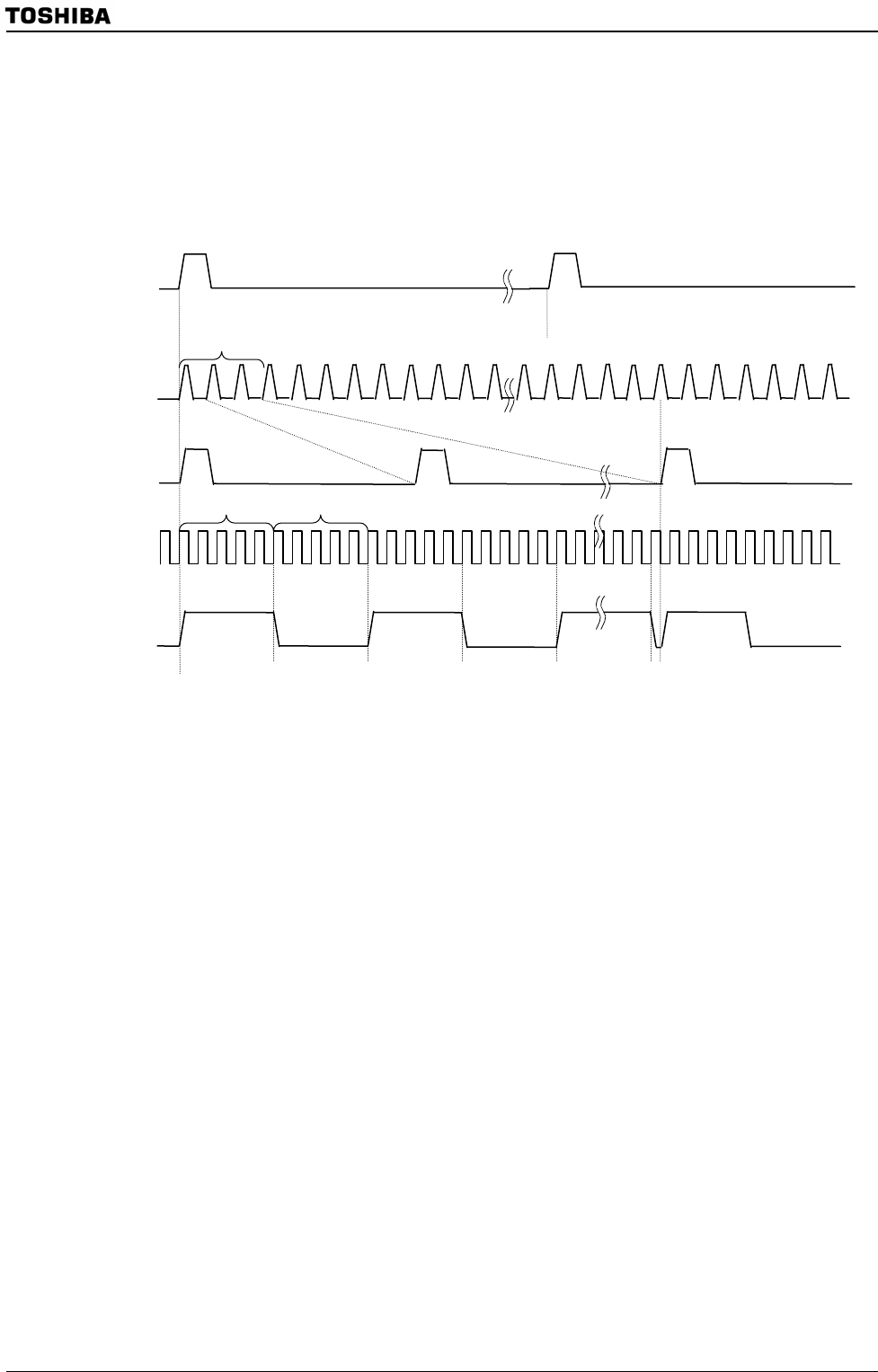

When LCDCTL0<FRMON>=1 and LCDCTL0<DLS>=1, frame output is inverted at

intervals set in LCDDVM0<FML3:0> and the LFR signal is inverted at intervals of

“LCP0 × M”. The “M” value is specified in LCDDVM0<FMP7:4>.

When <DLS>="1" LFR signal synchronous with front edge of LHSYNC signal.

So, prohibit to set <FREDGE>=1, always need to set <FREDGE>=0.

LVSYNC

LHSYNC

LHSYNC (Expansion)

LCP0

M M

N

LFR

<FREDGE>=0

<FRMON> = 1

<FMP7:0> = N

<FML7:0> = M

<DLS> = 1

Note prohibit to set <FREDGE>=1, always need to set <FREDGE>=0.