TMP92CZ26A

92CZ26A-445

(b) Dual packet mode

In dual packet mode, FIFO is divided into A and B packet, it is controlled

according to priority in hardware. It can be performed at once, transmitting and

receiving data to USB host and exchanges to external of UDC. When it reads out

data from FIFO for receiving, confirm condition of two packets, and consider the

order of priority. If it has received data to two packets, UDC outputs from first

receiving data by FIFO that can be accessed are common in two packets.

DATASIZE register is prepared every packet A and packet B. First, CPU must

recognize data number of first receiving packet by PACKET_ACTIVE bit. If

PACKET_ACTIVE bit was set to 1, that packet is received, first. Packet A and

packet B set data turn about always.

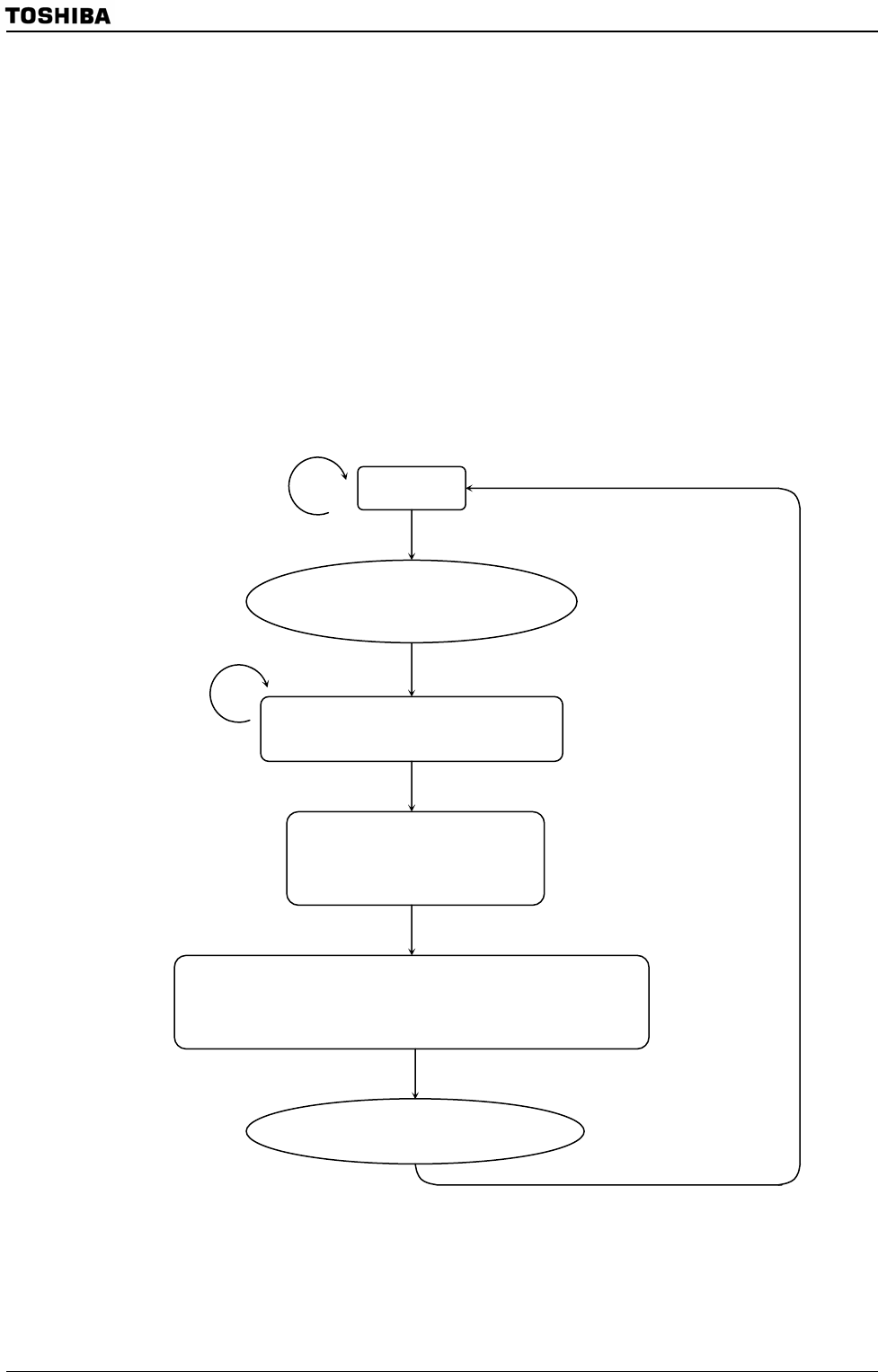

Below is this sequence.

Figure 3.16.17 Receiving Sequence in Dual Packet Mode

IDLE

DATASET register

• Check bit of EPx_DSET_A

• Check bit of EPx_DSET_B

SIZE register

• Confirm Size of SIZE_A_L

• Confirm Size of SIZE_A_H

• Confirm Size of SIZE_B_L

• Confirm Size of SIZE_B_H

• Read size of receiving data from applicable endpoint

• There is below 3 cases by setting bit of DATASET

Only A: Read number of sizeA register

Only B: Read number of sizeB register

Both of A and B: Read number of sizeA + B register

DATASET = 1

DATASET register

• Set bit of EPx_DSET_A (B)

• Assert EPx_DATASET signal

• Clear receiving data in FIFO

• Clear applicable bit in DATASET register

Interrupt by EPx_FULL_A (B)

Check DATASET register

Receiving valid data

DATASET = 0

Wait receiving data