TMP92CZ26A

92CZ26A-388

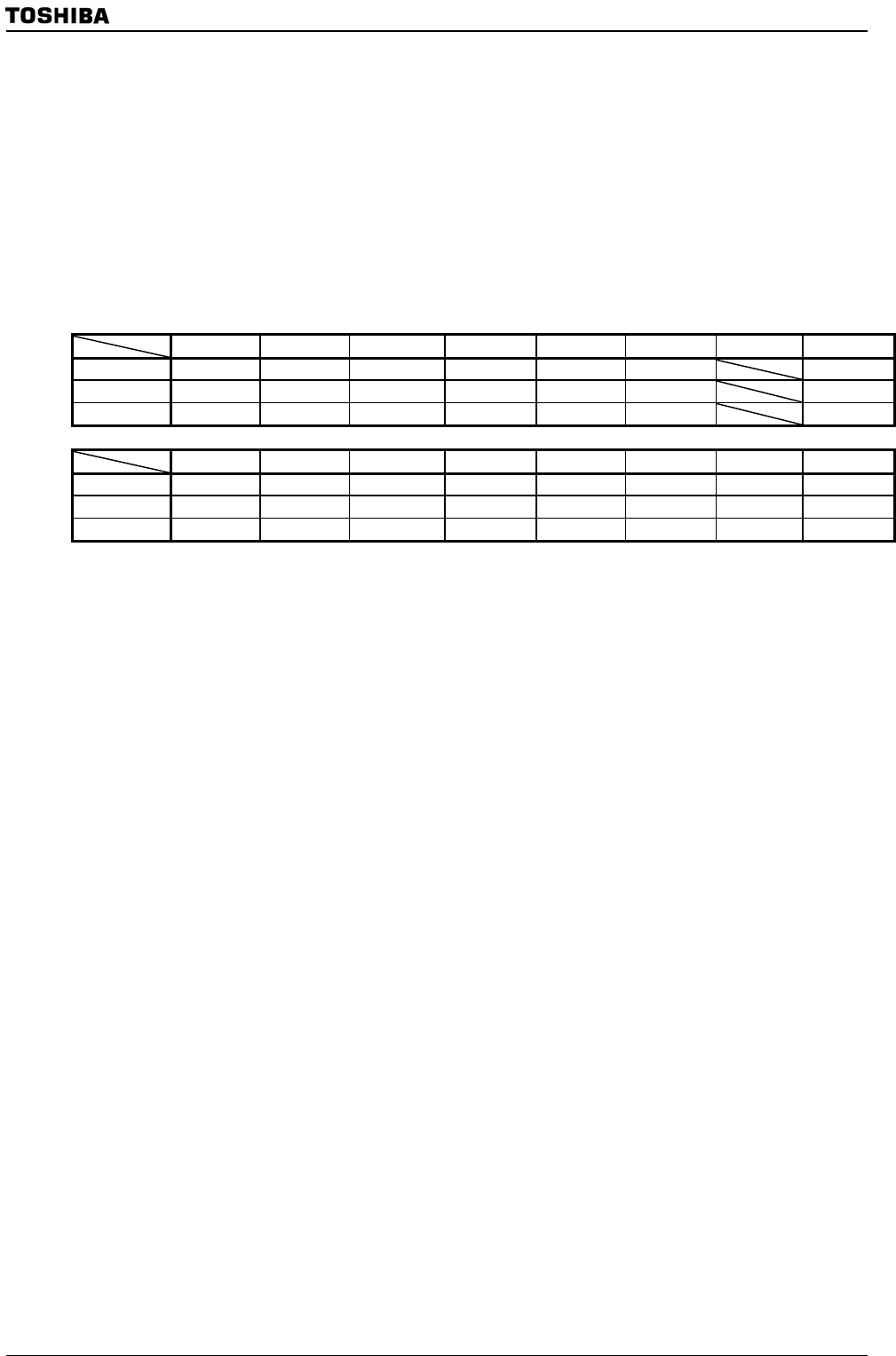

3.16.3.12 DATASET Register

This register shows whether FIFO has data or not.

The application program can be checked it by accessing this register that whether

FIFO has data or not.

In the receiving status, when valid data transfer from USB host finished, bit which

correspond to applicable endpoint is set to “1” and generate interrupt. And, when

application read data of 1-packet, this bit is cleared to “0”. In the transmitting status,

when it terminated that 1-packet data transfer to FIFO, this bit is set to “1”. And when

valid data is transferred to USB host, this bit is cleared to “0” and generates interrupt.

7 6 5 4 3 2 1 0

bit Symbol EP3_DSET_B EP3_DSET_A EP2_DSET_B EP2_DSET_A EP1_DSET_B EP1_DSET_A EP0_DSET_A

Read/Write R R R R R R R

After reset 0 0 0 0 0 0 0

7 6 5 4 3 2 1 0

bit Symbol EP7_DSET_B EP7_DSET_A EP6_DSET_B EP6_DSET_A EP5_DSET_B EP5_DSET_A EP4_DSET_B EP4_DSET_A

Read/Write R R R R R R R R

After reset 0 0 0 0 0 0 0 0

Note: DATASET1<EP3_DSET_B>, DATASET2 registers are not used at TMP92CZ26A.

• Single packet mode

(DATASET1: Bit0, bit2, bit4 and bit6 DATASET2: Bit0, bit2, bit4 and bit6)

These bits show whether FIFO of applicable endpoint has data or not.

In endpoint of receiving mode, if bit 1 of applicable endpoint is “1”, data that

should be read exist to FIFO. Access EPx_SIZE register, and grasp size of data

that should be read, and read data of its size. When this bit is “0”, data that

should be read does not exist.

In endpoint of transmitting mode, if bit of applicable endpoint is “0”, CPU can

be transferred data under the payload. If its bit is “1”, because of FIFO have

transfer waiting data, transfer data to FIFO in UDC after applicable bit was

cleared to “0”. When short-packet is transferred, access EOP register after

writing transmission data to applicable endpoint.

• Dual packet mode

(DATASET1: Bit3, bit5 and bit7 DATASET2: Bit1, bit3 bit5 and bit7)

These bits become effective in the dual packet mode. This mode has FIFO of

2-packets.

Each packet (called packet-A, packet-B) has DATASET-bit.

In isochroous transfer, it shows data transfer that can access in present frame

the packet. This is different from above one. In this case, the bit that whether A

or B is set to “1”, it is renewed according as shifting flame.

DATASET1

(07CCH)

DATASET2

(07CDH)