TMP92CZ26A

92CZ26A-36

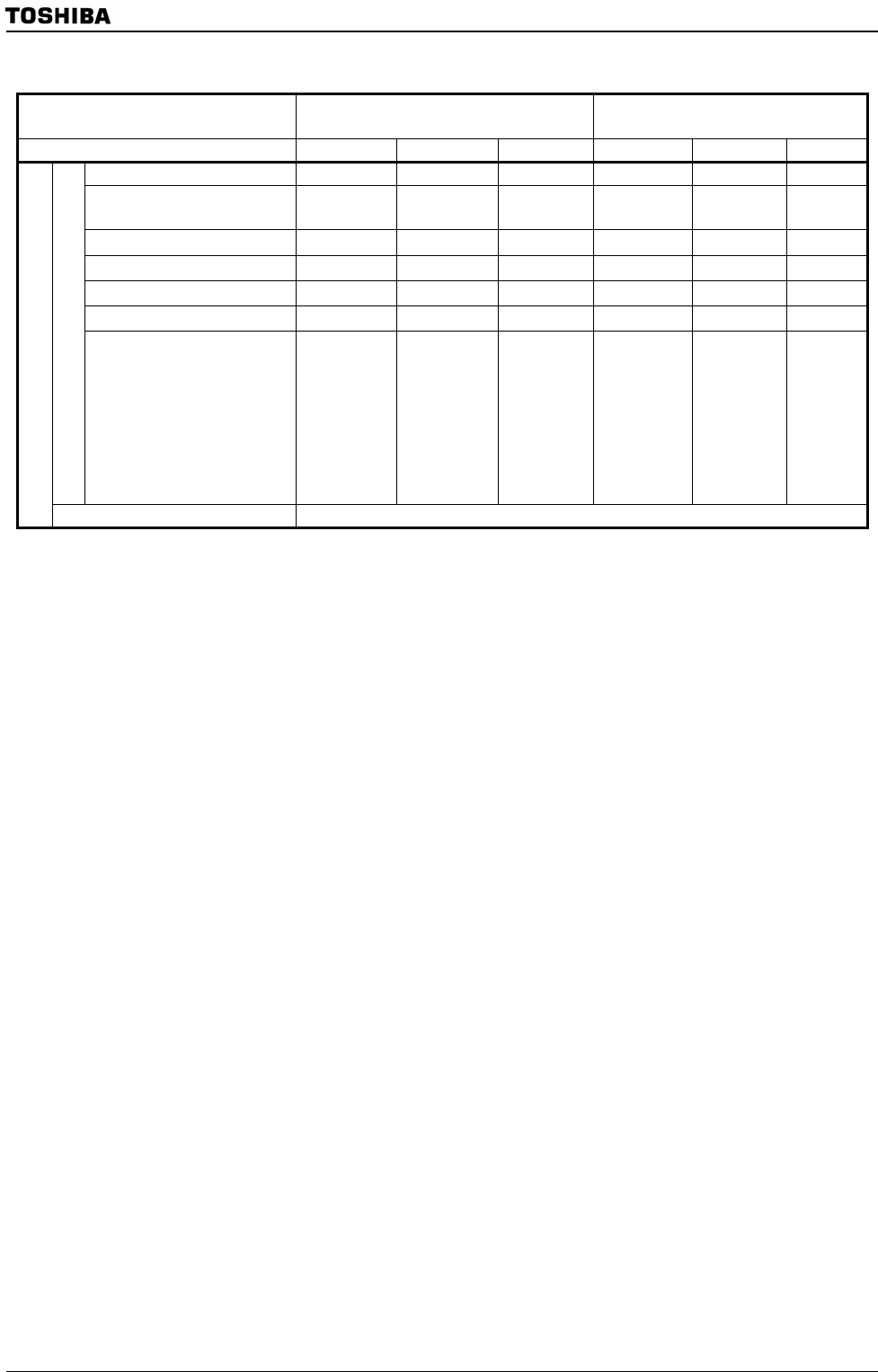

Table 3.3.4 Source of Halt state clearance and Halt clearance operation

Status of Received Interrupt

Interrupt Enabled

(interrupt level) ≥ (interrupt mask)

Interrupt Disabled

(interrupt level) < (interrupt mask)

Halt mode IDLE2 IDLE1 STOP IDLE2 IDLE1 STOP

INTWDT

× × − − −

INT0 to 5 (Note1)

INTKEY

*1

{ { {

*1

INTUSB

*2

× { {

*2

×

INT6 to 7(PORT) (Note1)

*1

{ { {

*1

INT6 to 7(TMRB)

× × × × ×

INTALM, INTRTC

× { { ×

Interrupt

INTTA0 to 7, INTTP0

INTTB00 to 01, INTTB10 to 11

INTRX,INTTX, INTSBI

INTI2S0 to 1, INTLCD,

INTAD, INTADHP

INTSPIRX,INTSPITX

INTRSC, INTRDY

INTDMA0 to 5

× × × × ×

Source of Halt state clearance

RESET Reset initializes the LSI

: After clearing the Halt mode, CPU starts interrupt processing.

{: After clearing the Halt mode, CPU resumes executing starting from instruction following the HALT instruction.

×: It can not be used to release the halt mode.

−: The priority level (interrupt request level) of non-maskable interrupts is fixed to 7, the highest priority level. There is

not this combination type.

*1: Releasing the halt mode is executed after passing the warmming-up time.

*2: 6 interrupts of all 24 INTUSB sources can release Halt state from IDLE1 mode. Therefore, the system of low

power dissipation can be built. However, the way of use is limited as below.

• Shift to IDLE1 mode :

Execute Halt instruction when the flag of INT_SUS or INT_CLKSTOP is “1” ( SUSPEND state )

• Release from IDLE1 mode :

Release Halt state by the request of INT_RESUME or INT_CLKON ( request of release SUSPEND )

Release Halt state by the request of INT_URST_STR or INT_URST_END ( request of RESET )

Note1: When the Halt mode is cleared by an INT0 interrupt of the level mode in the interrupt enabled status, hold level

H until starting interrupt processing. If level L is set before holding level L, interrupt processing is correctly

started.