TMP92CZ26A

92CZ26A-222

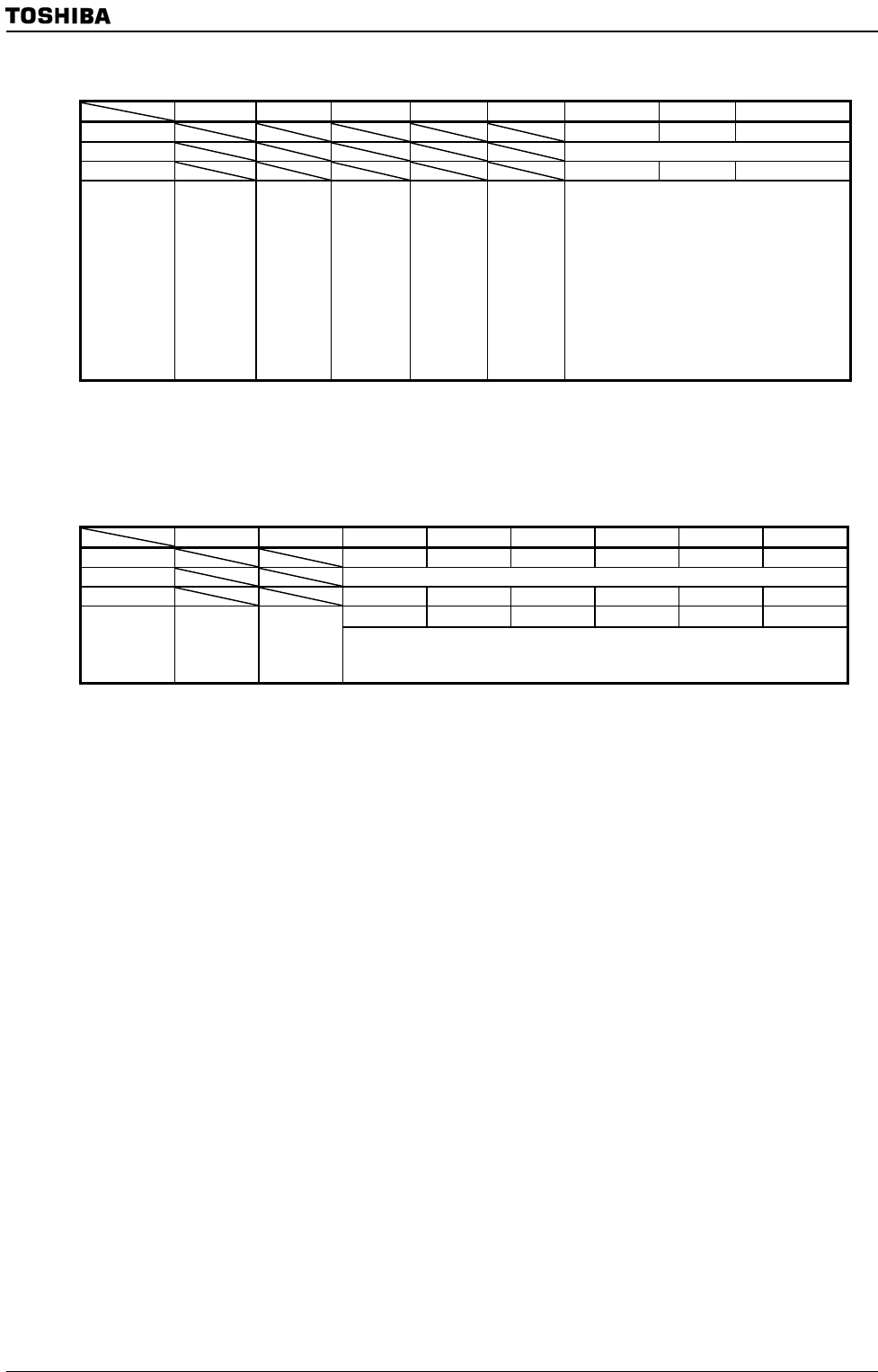

SDRAM Command Register

7 6 5 4 3 2 1 0

Bit symbol SCMM2 SCMM1 SCMM0

Read/Write R/W

After reset 0 0 0

Function

Command issue

(Note 1) (Note 2)

000: Don’t care

001: Initialization sequence

a. Precharge All command

b. Eight Auto Refresh commands

c. Mode Register Set command

010: Precharge All command

100: Reserved

101: Self Refresh Entry command

110: Self Refresh Exit command

Others: Reserved

Note 1: <SCMM2:0> is automatically cleared to “000” after the specified command is issued. Before writing the next

command, make sure that <SCMM2:0> is “000”. In the case of the Self Refresh Entry command, however,

<SCMM2:0> is not cleared to “000” by execution of this command. Thus, this register can be used as a flag for

checking whether or not Self Refresh is being performed.

Note 2: The Self Refresh Exit command can only be specified while Self Refresh is being performed.

SDRAM HDMA Burst Length Select Register

7 6 5 4 3 2 1 0

Bit symbol SDBL5 SDBL4 SDBLS SDBL2 SDBL1 SDBL0

Read/Write R/W

After reset 0 0 0 0 0 0

For HDMA5 For HDMA4 For HDMA3 For HDMA2 For HDMA1 For HDMA0

Function

HDMA burst length

0: 1 Word read / Single write

1: Full page read / Burst write

Figure 3.10.1 Control Registers

SDCMM

(0253H)

SDBLS

(0254H)