TMP92CZ26A

92CZ26A-69

3.5.1 General-purpose Interrupt Processing

When the CPU accepts an interrupt, it usually performs the following sequence of

operations. However, in the case of software interrupts and illegal instruction interrupts

generated by the CPU, the CPU skips steps (1) and (3), and executes only steps (2), (4), and

(5).

(1) The CPU reads the interrupt vector from the interrupt controller. When more than one

interrupt with the same priority level have been generated simultaneously, the

interrupt controller generates an interrupt vector in accordance with the default

priority and clears the interrupt requests. (The default priority is determined as

follows: The smaller the vector value, the higher the priority.)

(2) The CPU pushes the program counter (PC) and status register (SR) onto the top of the

stack (Pointed to by XSP).

(3) The CPU sets the value of the CPU’s interrupt mask register <IFF2:0> to the priority

level for the accepted interrupt plus 1. However, if the priority level for the accepted

interrupt is 7, the register’s value is set to 7.

(4) The CPU increments the interrupt nesting counter INTNEST by 1.

(5) The CPU jumps to the address given by adding the contents of address FFFF00H + the

interrupt vector, then starts the interrupt processing routine.

On completion of interrupt processing, the RETI instruction is used to return control

to the main routine. RETI restores the contents of the program counter and the status

register from the stack and decrements the interrupt nesting counter INTNEST by 1.

Non-maskable interrupts cannot be disabled by a user program. Maskable interrupts,

however, can be enabled or disabled by a user program. A program can set the priority

level for each interrupt source. (A priority level setting of 0 or 7 will disable an interrupt

request.) If an interrupt request is received for an interrupt with a priority level equal to

or greater than the value set in the CPU interrupt mask register <IFF2:0>, the CPU will

accept the interrupt. The CPU interrupt mask register <IFF2:0> is then set to the value

of the priority level for the accepted interrupt plus 1.

If during interrupt processing, an interrupt is generated with a higher priority than the

interrupt currently being processed, or if, during the processing of a non-maskable

interrupt processing, a non-maskable interrupt request is generated from another source,

the CPU will suspend the routine which it is currently executing and accept the new

interrupt. When processing of the new interrupt has been completed, the CPU will resume

processing of the suspended interrupt.

If the CPU receives another interrupt request while performing processing steps (1) to

(5), the new interrupt will be sampled immediately after execution of the first instruction

of its interrupt processing routine. Specifying DI as the start instruction disables nesting

of maskable interrupts.

After a reset, initializes the interrupt mask register <IFF2:0> to 111, disabling all

maskable interrupts.

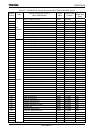

Table 3.5.1 shows the TMP92CZ26A interrupt vectors and micro DMA start vectors.

FFFF00H to FFFFFFH (256 bytes) is designated as the interrupt vector area.