TMP92CZ26A

92CZ26A-493

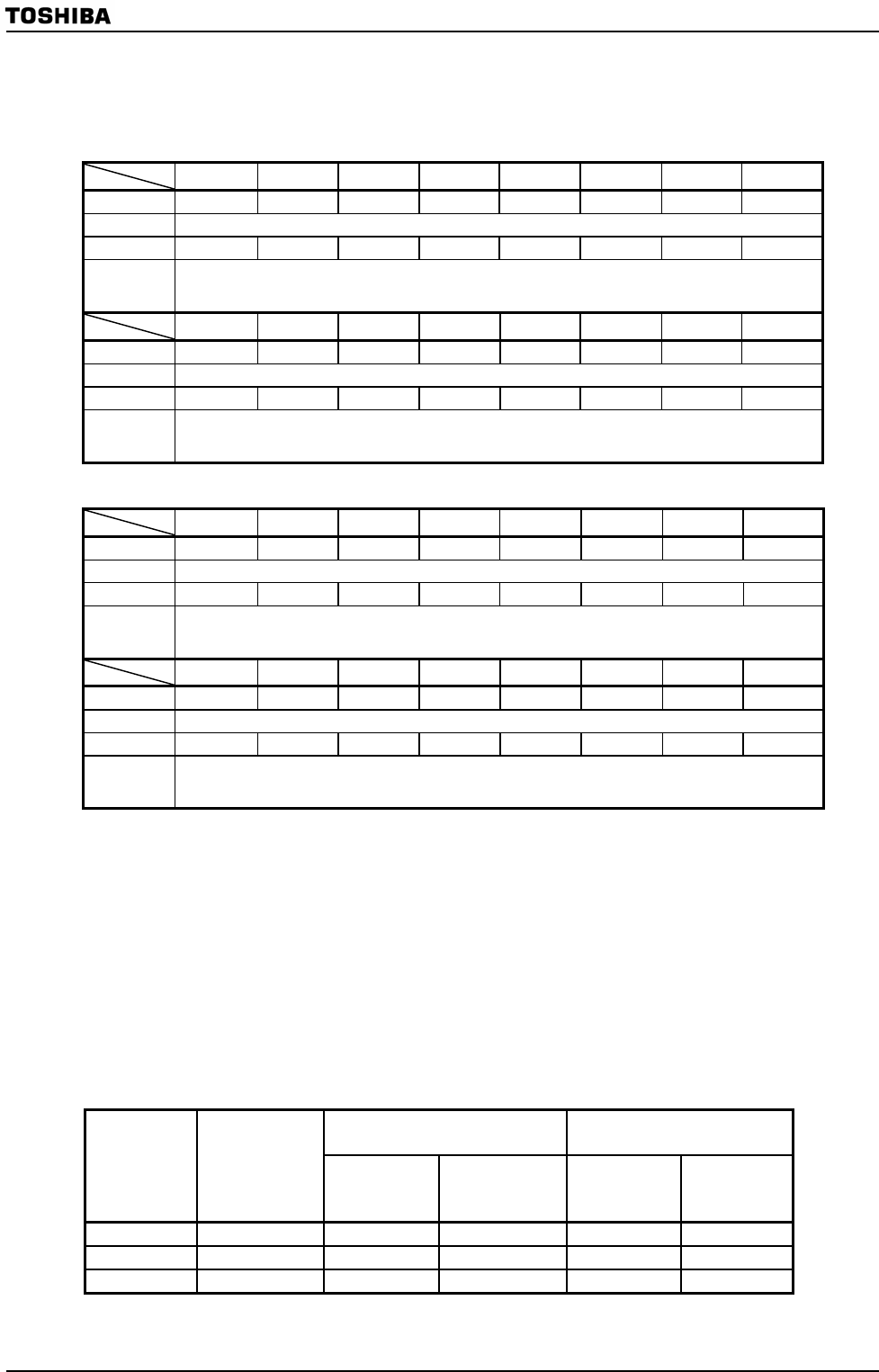

(5) SPITD (SPI Transmit Data Register)

SPITD0, SPITD1 registers are for writing transmitted data.

SPITD0 Register

7 6 5 4 3 2 1 0

bit Symbol

TXD7 TXD6 TXD5 TXD4 TXD3 TXD2 TXD1 TXD0

Read/Write

R/W

After reset

0 0 0 0 0 0 0 0

Function

Transmit data register [7:0]

15 14 13 12 11 10 9 8

bit Symbol

TXD15

TXD14 TXD13 TXD12 TXD11 TXD10 TXD9 TXD8

Read/Write

R/W

After reset

0 0 0 0 0 0 0 0

Function

Transmit data register [15:8]

SPITD1 Register

7 6 5 4 3 2 1 0

bit Symbol

TXD7 TXD6 TXD5 TXD4 TXD3 TXD2 TXD1 TXD0

Read/Write

R/W

After reset

0 0 0 0 0 0 0 0

Function

Transmit data register [7:0]

15 14 13 12 11 10 9 8

bit Symbol

TXD15

TXD14 TXD13 TXD12 TXD11 TXD10 TXD9 TXD8

Read/Write

R/W

After reset

0 0 0 0 0 0 0 0

Function

Transmit data register [15:8]

Figure 3.17.12 SPITD Register

This bit is for writing transmitted data. When read, the last written data is read. The data is

overwritten if write next data with transmit FIFO is not empty.

Transmit register exist 4bytes. Therefore, it is possible writing by using 4byte instruction

(use DMA together it etc.)

However, when write data (Destination address), writing the data from 830 addresses is

always needed.

Method of writing data (instruction) is restricted. Please refer to following table.

UNIT transmission

(No using FIFO)

Sequential transmission

(Using FIFO)

Transmit

data

write size

Instruction

example

1byte

transmission

<unit16>=0

2 byte

transmission

<unit16>=1

1 byte

transmission

<unit16>=0

2 byte

transmission

<unit16>=1

1byte write ld (0x830),a

Prohibit

2byte write ld (0x830),wa

4byte write ld (0x830),xwa

: All data that written by CPU is transmitted

: Invalid data that except for written by CPU is transmitted

SPITD0

(830H)

(831H)

SPITD1

(832H)

(833H)