TMP92CZ26A

92CZ26A-383

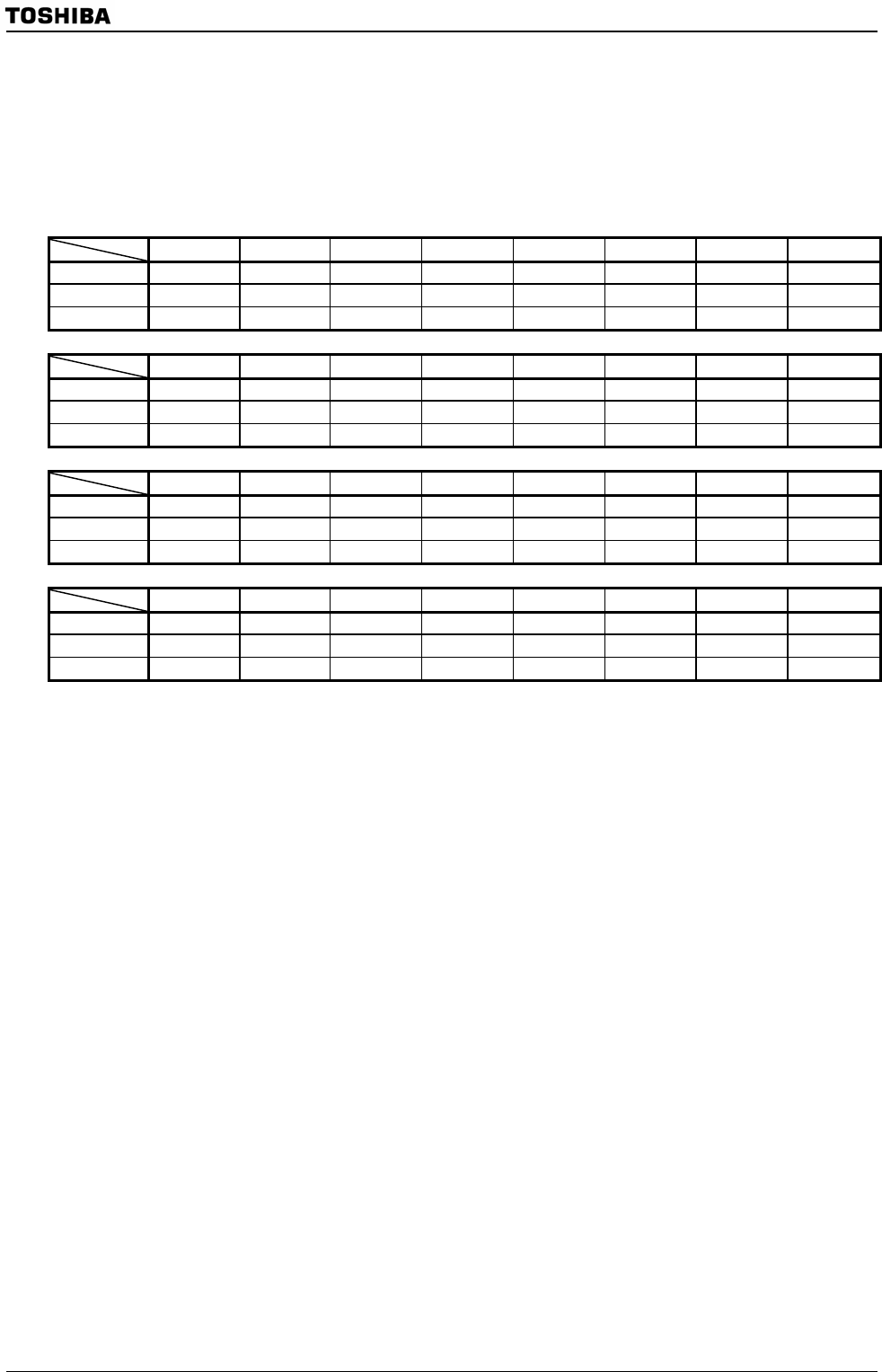

3.16.3.2 EPx_FIFO Register (x: 0 to 3)

This register is prepared for each endpoint independently.

This is the window register from or to FIFO RAM.

In the auto bus enumeration, the request controller in UDC set mode, which is

defined at endpoint descriptor for each endpoint automatically. By this, each endpoint

is set to voluntary direction.

7 6 5 4 3 2 1 0

bit Symbol EP0_DATA7 EP0_DATA6 EP0_DATA5 EP0_DATA4 EP0_DATA3 EP0_DATA2 EP0_DATA1 EP0_DATA0

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

After reset Undefined Undefined Undefined Undefined Undefined Undefined Undefined Undefined

7 6 5 4 3 2 1 0

bit Symbol EP1_DATA7 EP1_DATA6 EP1_DATA5 EP1_DATA4 EP1_DATA3 EP1_DATA2 EP1_DATA1 EP1_DATA0

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

After reset Undefined Undefined Undefined Undefined Undefined Undefined Undefined Undefined

7 6 5 4 3 2 1 0

bit Symbol EP2_DATA7 EP2_DATA6 EP2_DATA5 EP2_DATA4 EP2_DATA3 EP2_DATA2 EP2_DATA1 EP2_DATA0

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

After reset Undefined Undefined Undefined Undefined Undefined Undefined Undefined Undefined

7 6 5 4 3 2 1 0

bit Symbol EP3_DATA7 EP3_DATA6 EP3_DATA5 EP3_DATA4 EP3_DATA3 EP3_DATA2 EP3_DATA1 EP3_DATA0

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

After reset Undefined Undefined Undefined Undefined Undefined Undefined Undefined Undefined

Note: Read or write these window registers by using load instruction of 1 byte because of each register have only 1

byte address. Don’t use load instruction of 2 bytes or 4 bytes.

The device request that received from the USB host is stored to following 8-byte

registers.

The 8-byte registers are bmRequestType, bRequest, wValue_L, wValue_H,

wIndex_L, wIndex_H, wLength_L and wLength_H. They are updated whenever new

SETUP token is received from host...

When the UDC receive without error, INT_SETUP interrupt is asserted and it

means the new device request has been received.

And there is a request which is operated automatically by UDC. It depends on

received request.

In that case, the UDC don’t assert INT_SETUP interrupt. A request which the UDC

is operating now can be checked by reading STANDARD_REQUEST_FLAG and

REQUEST_FLAG.

Endpoint0

(0780H)

Endpoint1

(0781H)

Endpoint2

(0782H)

Endpoint3

(0783H)