TMP92CZ26A

92CZ26A-242

3.11.3 ECC Control

NAND Flash memory devices may inherently include error bits. It is therefore necessary to

implement the error correction processing using ECC (Error Correction Code).

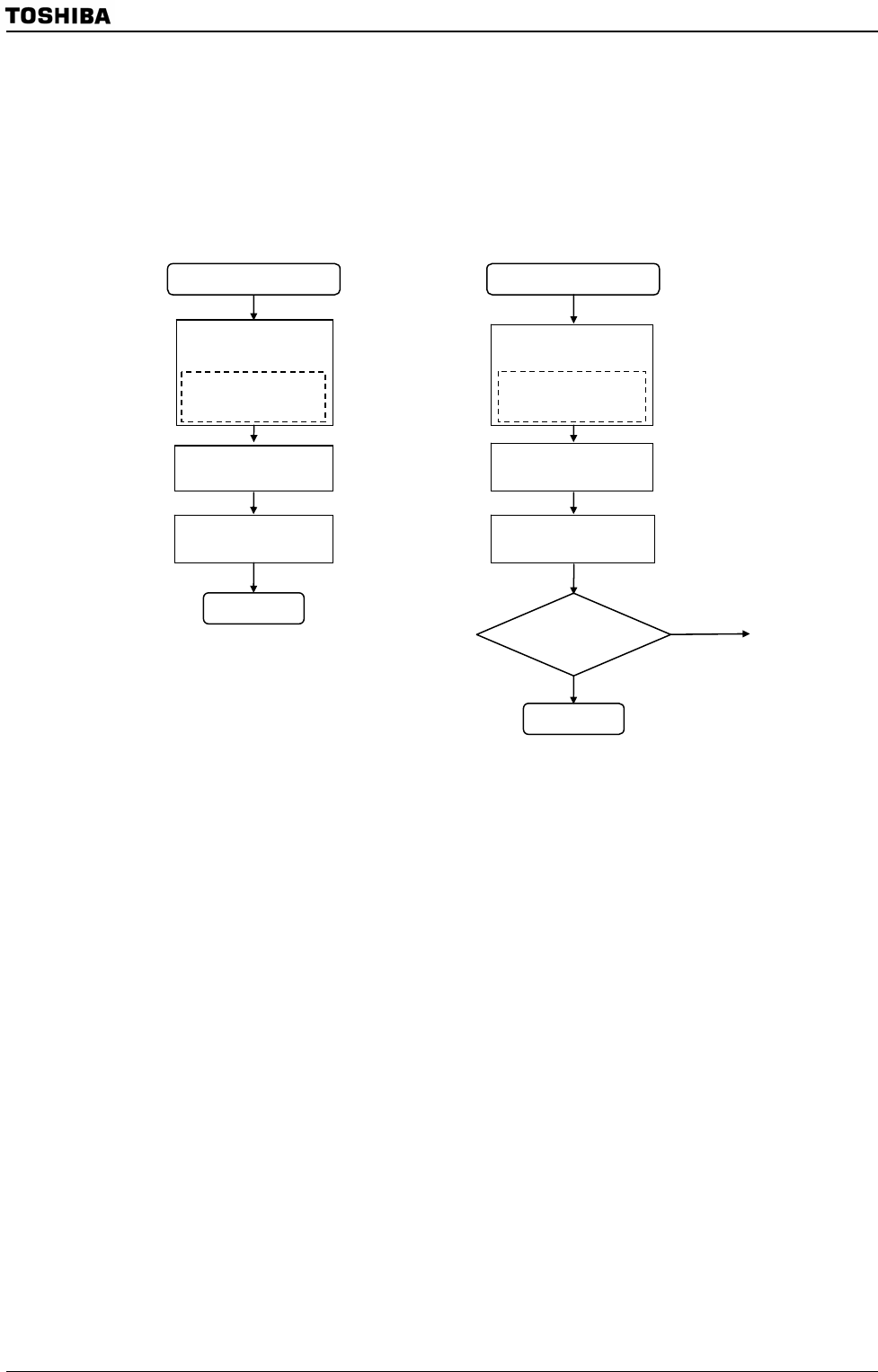

Figure 3.11.4 shows a basic flowchart for ECC control.

Figure 3.11.4 Basic Flow of ECC Control

Write:

1. When data is written to the actual NAND Flash memory, the ECC generator in

the NDFC simultaneously generates ECC for the written data.

2. The ECC is written to the redundant area in the NAND Flash separately from

the valid data.

Read:

1. When data is read from the actual NAND Flash memory, the ECC generator in

the NDFC simultaneously generates ECC for the read data.

2. The ECC for the written data and the ECC for the read data are compared to

detect and correct error bits.

Valid data write to

NAND Flash

END

Data Write Data Read

Valid data write to

ECC generator

Write ECC to

NAND Flash

Valid data read from

NAND Flash

END

ECC read from

NAND Flash

ECC read

from ECC

g

enerato

r

ECC read from

ECC circuit

Is there error?

Yes

No

Valid data write to

ECC generator

Error correction

p

rocess