TMP92CZ26A

92CZ26A-620

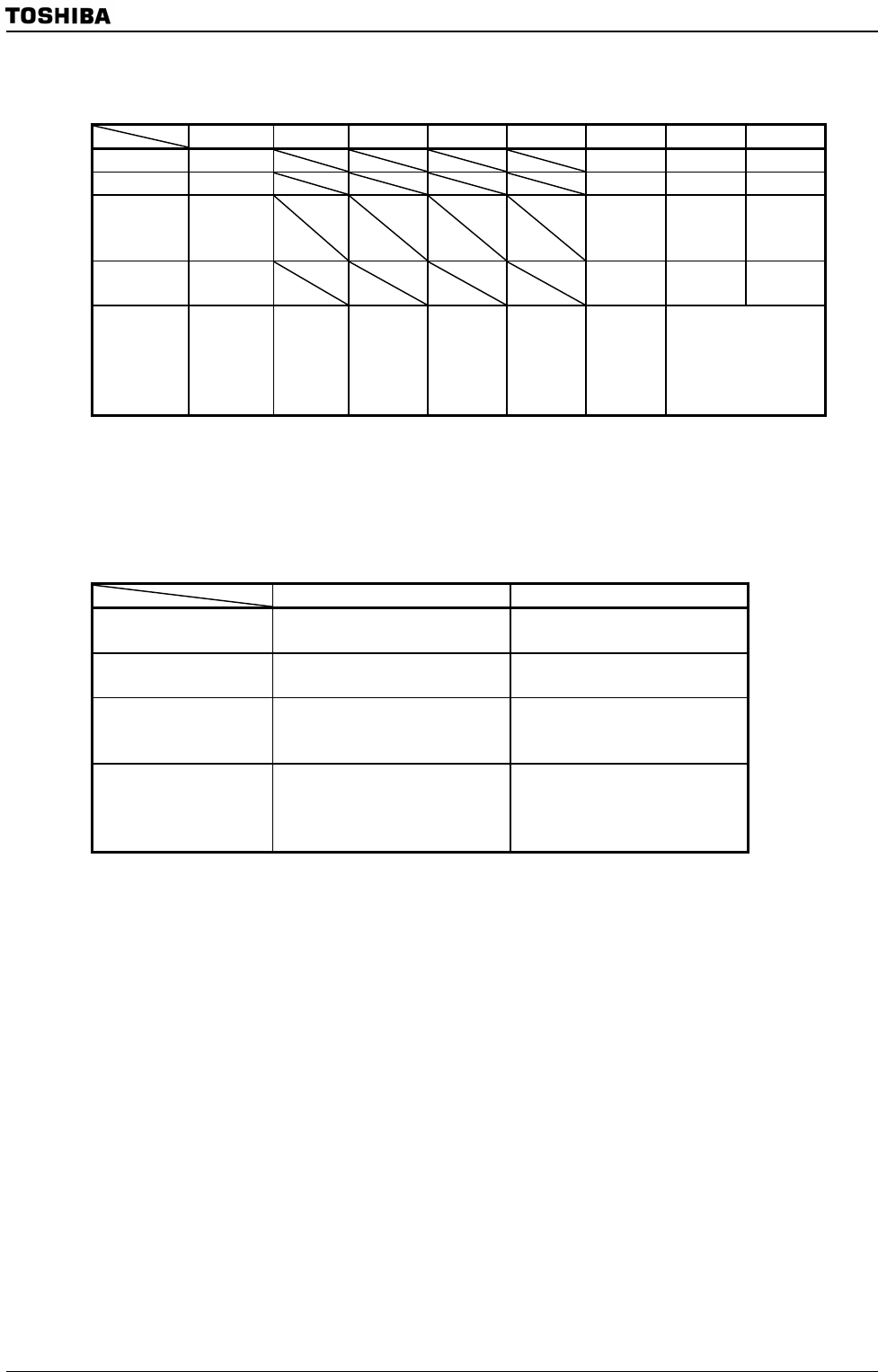

3.25.1 SFR

7 6 5 4 3 2 1 0

bit symbol PCM_ON

−

WUTM1 WUTM0

Read/Write R/W W R/W R/W

After

system

reset

0 0 0 0

After hot

reset

Data

retained

−

Data

retained

Data

retained

Function

Power

Cut Mode

0: Disable

1: Enable

Always

write “0”

Always

read as “0”

Warm-up time

00: 29 (15.625 ms)

01: 210 (31.25 ms)

10: 211 (62.5 ms)

11: 212 (125 ms)

Note: After wake-up interruption, internal wake-up timer count setting register value:<WUTM1:0>, and after about

77us, external PWE terminal change from low level to high level. Additionally after more about 92us, internal

reset signal will be released. We recommend to confirm actual performance on final set, because the time to

be stable all voltage level and power supply circuit are difference characteristics every final set.

The following operations are affected by the setting of the <PCM_ON> bit.

PCM_ON = 1 PCM_ON = 0

External interrupt input

No interrupt

HOT_RESET signal assert

Interrupt

Operation after reset

−

Startup depending on the AM1

and AM0 pins

Operation after hot reset

Startup from boot ROM regardless

of the AM1 and AM0 pins and

jump to internal RAM area.

−

Warm-up counter

A change in the PWE pin level is

used as a trigger to start counting

the low-frequency clock for

releasing HOT_RESET.

Counter stopped

PMCCTL

(02F0H)