TMP92CZ26A

92CZ26A-156

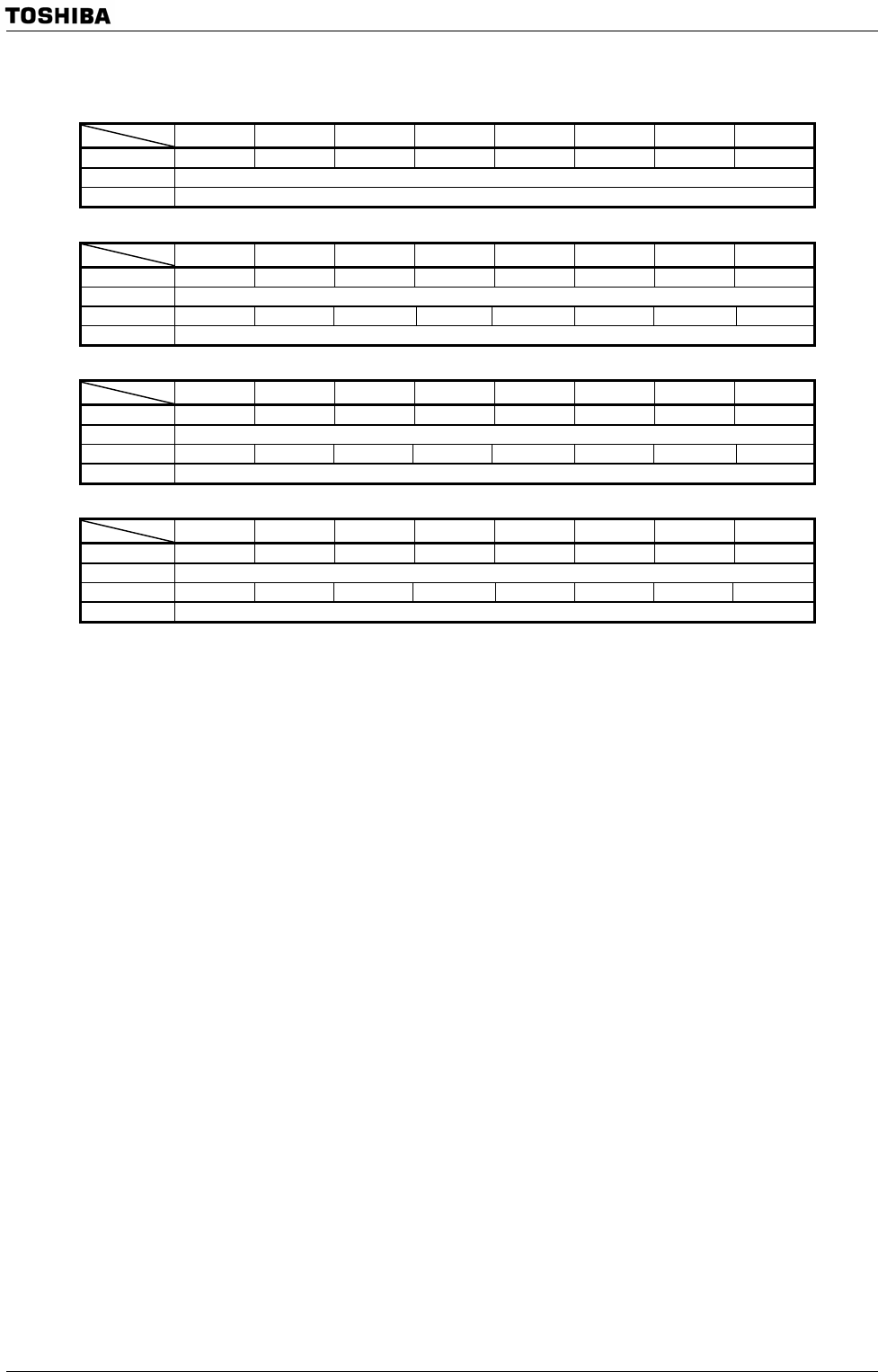

Port N register

7 6 5 4 3 2 1 0

bit Symbol PN7 PN6 PN5 PN4 PN3 PN2 PN1 PN0

Read/Write R/W

After reset Data from external port (Output latch register is set to “1”)

Port N control register

7 6 5 4 3 2 1 0

bit Symbol PN7C PN6C PN5C PN4C PN3C PN2C PN1C PN0C

Read/Write W

After reset 0 0 0 0 0 0 0 0

Function 0: Input 1: Output

Port N function register

7 6 5 4 3 2 1 0

bit Symbol PN7F PN6F PN5F PN4F PN3F PN2F PN1F PN0F

Read/Write W

After reset 0 0 0 0 0 0 0 0

Function 0: CMOS output 1: Open-drain output

Port N drive register

7 6 5 4 3 2 1 0

bit Symbol PN7D PN6D PN5D PN4D PN3D PN2D PN1D PN0D

Read/Write R/W

After reset 1 1 1 1 1 1 1 1

Function Input/Output buffer drive register for standby mode

Note 1: Read-Modify-Write is prohibited for the registers PNCR and PNFC.

Figure 3.7.43 Register for Port N

PNCR

(005EH)

PN

(005CH)

PNDR

(0097H)

PNFC

(005FH)