TMP92CZ26A

92CZ26A-168

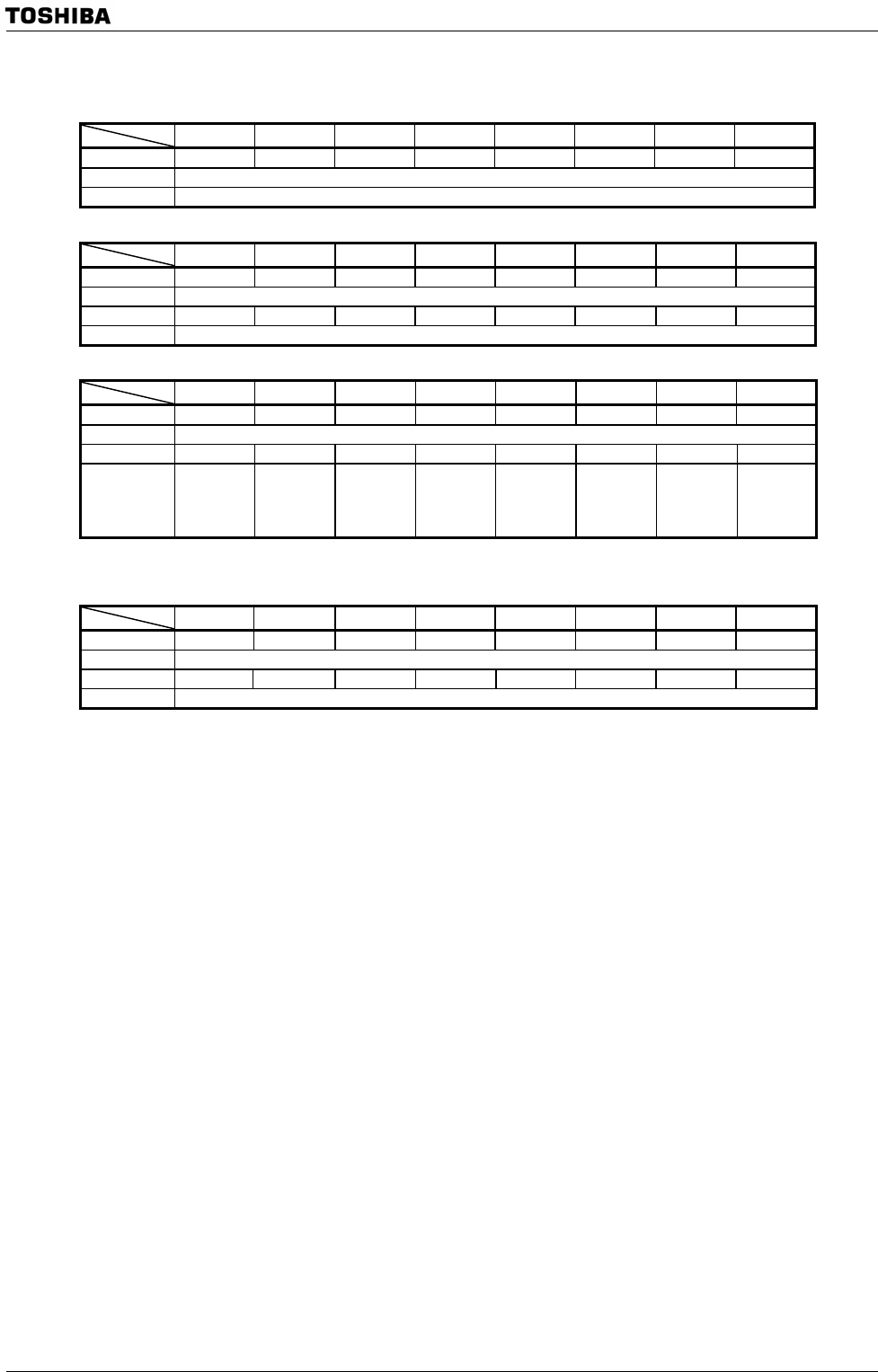

Port U register

7 6 5 4 3 2 1 0

Bit Symbol PU7 PU6 PU5 PU4 PU3 PU2 PU1 PU0

Read/Write R/W

After reset Data from external port (Output latch register is cleared to “0”)

Port U control register

7 6 5 4 3 2 1 0

Bit Symbol PU7C PU6C PU5C PU4C PU3C PU2C PU1C PU0C

Read/Write W

After reset 0 0 0 0 0 0 0 0

Function 0: Input 1: Output

Port U function register

7 6 5 4 3 2 1 0

Bit Symbol PU7F PU6F PU5F PU4F PU3F PU2F PU1F PU0F

Read/Write W

After reset 0 0 0 0 0 0 0 0

Function 0: Port

1: LD23

0: Port

1: LD22

0: Port

1:

LD21@

<PU5C>=1

0: Port

1: LD20

0: Port

1: LD19

0: Port

1: LD18

0: Port

1: LD17

0: Port

1: LD16

Note: When PU is used as LD23 to LD16, set applicable PUnC to “1”.

Port U drive register

7 6 5 4 3 2 1 0

Bit Symbol PU7D PU6D PU5D PU4D PU3D PU2D PU1D PU0D

Read/Write R/W

After reset 1 1 1 1 1 1 1 1

Function Input/Output buffer drive register for standby mode

Note1: Read-Modify-Write is prohibited for the registers PUCR, PUFC.

Note2: When use PU as LD23 to LD16, set PUnC to “1”. When use PU5 as LD21, set PU5C to “1”.

Figure 3.7.56 Register for Port U

PU

(00A4H)

PUFC

(00A7H)

PUCR

(00A6H)

PUDR

(009CH)