TMP92CZ26A

92CZ26A-29

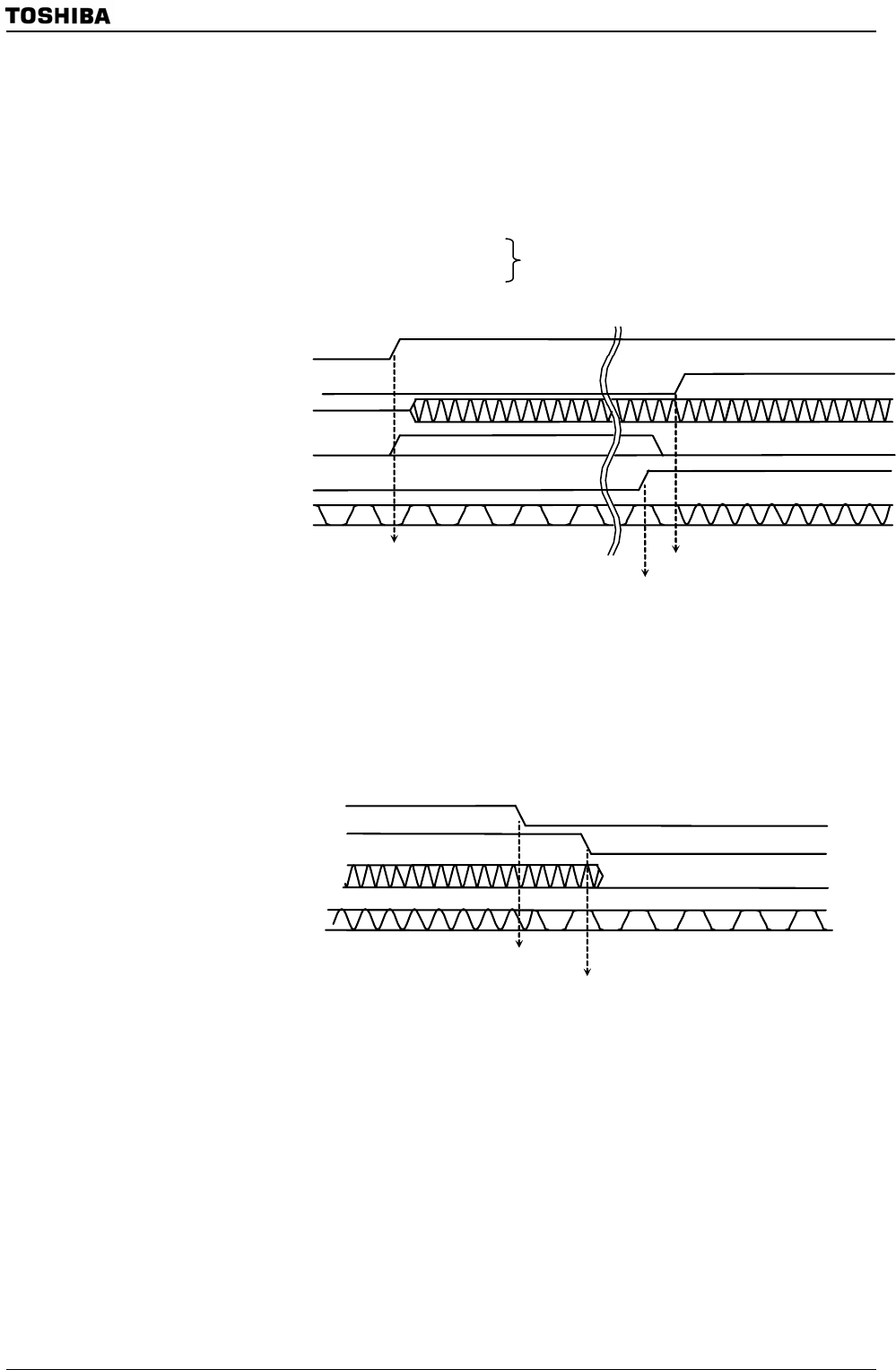

The following is a setting example for PLL0-starting and PLL0-stopping.

(Example-1) PLL0-starting

PLLCR0 EQU 10E8H

PLLCR1 EQU 10E9H

LD (PLLCR1),1XXXXXXXXB ;

Enables PLL0 operation and starts lock-up

.

LUP: BIT 5,(PLLCR0) ;

JR Z,LUP ;

Detects end of lock-up

LD (PLLCR0), X1XXXXXXB ; Changes fc from 10 MHz to 60 MHz.

X: Don't care

Counts up by f

OSCH

During lock-up

<PLL0>

PLL output: f

PLL

Lockup timer

<LUPFG>

System clock f

SYS

Starts PLL0 operation and

Starts lock-up.

Ends of lock-up

Changes from 10MHz to 60MHz.

A

fter lock-up

<FCSEL>

(Example-2) PLL0-stopping

PLLCR0 EQU 10E8H

PLLCR1 EQU 10E9H

LD (PLLCR0),X0XXXXXXB ; Changes fc from 60 MHz to10 MHz.

LD (PLLCR1),0XXXXXXXB ; Stop PLL

X: Don't care

<PLL0>

PLL0 output: f

PLL

System clock f

SYS

Stops PLL0 operation .

Changes from 60MHz to 10 MHz.

<FCSEL>

Note) PLL1 operates as well.