Receive and Transmit Description — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 101

5.0 Receive and Transmit Description

This section describes the data flows, packet reception, packet transmission, transmit descriptor ring

structure, TCP segmentation, and transmit checksum offloading for the 82575.

5.1 82575 Data Flows

5.1.1 Transmit Data Flow

Transmit data flow provides a high level description of all data/control transformations steps needed for

transmitting Ethernet packets over the wire.

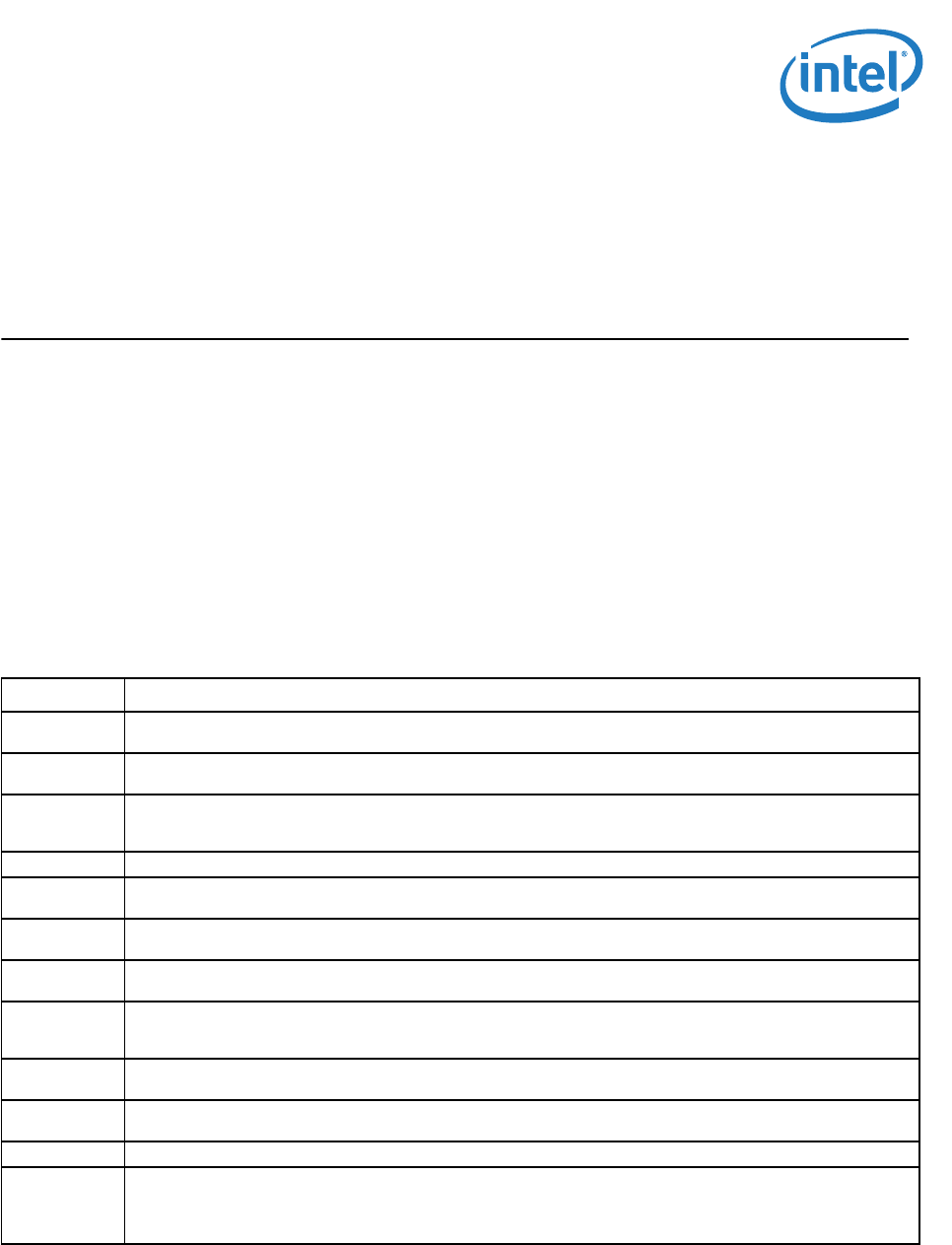

Step Description

1 The host creates a descriptor ring and configures one of the 82575’s transmit queues with the address location,

length, head and tail pointers of the ring (one of four available transmit queues).

2 The host is requested by the TCP/IP stack to transmit a packet; it gets the packet data within one or more data

buffers.

3 The host initializes descriptor(s) that point to the data buffer(s) and have additional control parameters that

describes the needed hardware functionality. The host places that descriptor in the correct location at the

appropriate transmit ring.

4 The host updates the appropriate queue tail pointer (TDT)

5 The 82575’s DMA senses a change of a specific TDT and as a result sends a PCIe* request to fetch the

descriptor(s) from host memory.

6 The descriptor(s) content is received in a PCIe* read completion and is written to the appropriate location in

the descriptor queue internal cache.

7 The DMA fetches the next descriptor and processes its content; as a result the DMA sends PCIe* requests to

fetch the packet data from system memory.

8 The packet data is being received from PCIe* completions and passes through the transmit DMA that performs

all programmed data manipulations (various CPU offloading tasks as checksum offload TSO offload, etc.) on the

packet data on the fly.

9 While the packet is passing through the DMA, it is stored into the transmit FIFO. After the entire packet is

stored in the transmit FIFO, it is being forwarded to transmit switch module.

10 The transmit switch arbitrates between host and management packets and eventually forwards the packet to

the MAC.

11 The MAC appends the L2 CRC to the packet and sends the packet to the line using a pre-configured interface.

12 When all the PCIe* completions for a given packet are done; the DMA updates the appropriate descriptor(s).