Intel

®

82575EB Gigabit Ethernet Controller — Interrupt Mask Set/Read Register - IMS (000D0h;

R/W)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

342 January 2011

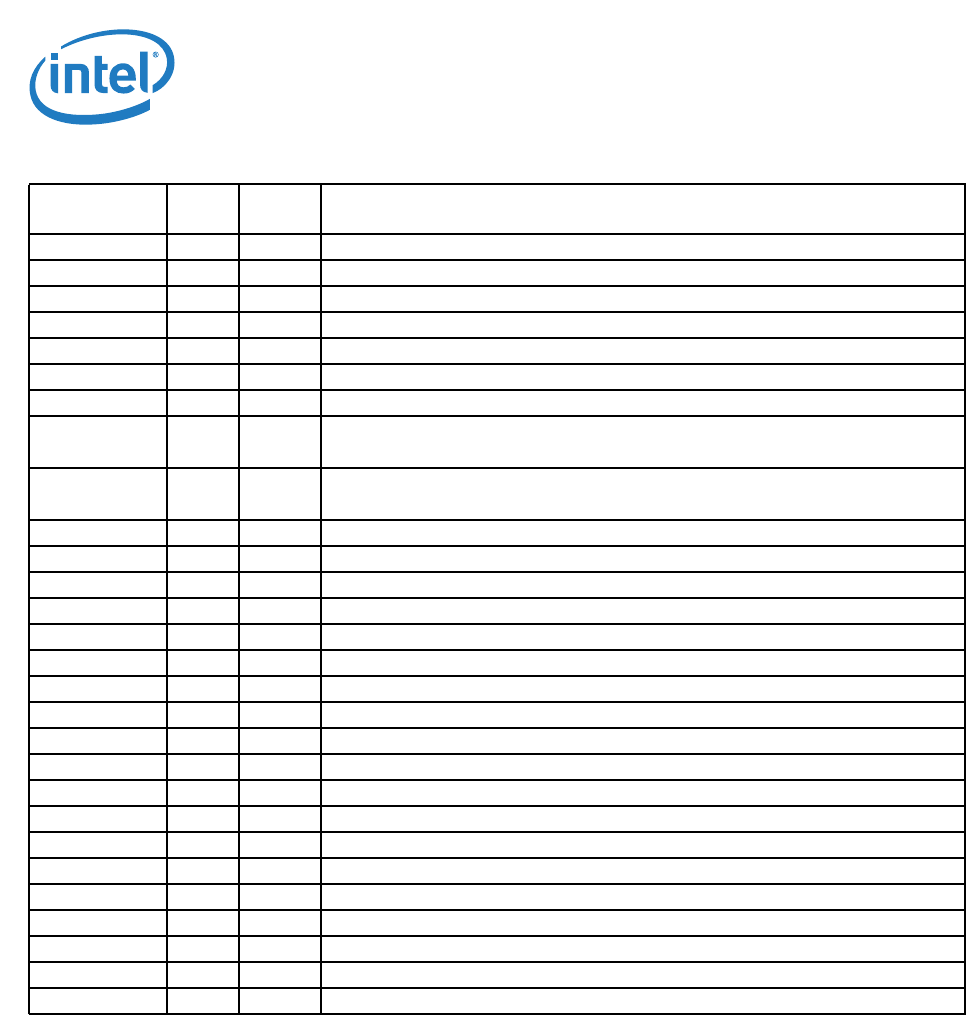

14.3.36 Interrupt Mask Set/Read Register - IMS

(000D0h; R/W)

Reading this register returns bits have an interrupt mask set. An interrupt is enabled if its

corresponding mask bit is set to 1b and disabled if its corresponding mask bit is set to 0b. A PCIe*

interrupt is generated each time one of the bits in this register is set and the corresponding interrupt

condition occurs. The occurrence of an interrupt condition is reflected by having a bit set in the

Interrupt Cause Read Register (see Section 14.3.34).

A particular interrupt can be enabled by writing a 1b to the corresponding mask bit in this register. Any

bits written with a 0b are unchanged. As a result, if software desires to disable a particular interrupt

condition that had been previously enabled, it must write to the Interrupt Mask Clear Register (see

Section 14.3.37) rather than writing a 0b to a bit in this register.

Field Bit(s)

Initial

Value

Description

TXDW 0 0b Sets the Transmit Descriptor Written Back Interrupt.

Reserved 1 - Reserved

LSC 2 0b Sets the Link Status Change Interrupt.

RXSEQ 3 0b Sets the Receive Sequence Error Interrupt.

RXDMT0 4 0b Sets the Receive Descriptor Minimum Threshold Hit Interrupt.

Reserved 5 0b Reserved.

RXO 6 0b Sets the Receiver Overrun Interrupt. Sets on Receive Data FIFO Overrun.

RXDW 7 0b Receiver Descriptor Write Back

Set when the 82575 writes back an Rx descriptor to memory.

Reserved 8 0b Reserved

Reads as 0b.

MDAC 9 0b Sets the MDI/O Access Complete Interrupt.

RXCFG 10 0b Sets the Receiving /C/ Ordered Sets Interrupt.

GPI_SDP0 11 0b Sets the General Purpose Interrupt, related to SDP0 pin.

GPI_SDP1 12 0b Sets the General Purpose Interrupt, related to SDP1 pin.

GPI_SDP2 13 0b Sets the General Purpose Interrupt, related to SDP2 pin.

GPI_SDP3 14 0b Sets the General Purpose Interrupt, related to SDP3 pin.

Reserved 17:15 0b Reserved.

MNG 18 0b Sets the Management Event Interrupt.

Reserved 19 0b Reserved.

OMED 20 0b Sets the Other Media Energy Detected Interrupt.

Reserved 21 0b Reserved.

RX PBUR 22 0b Sets the Receive Packet Buffer Unrecoverable Error Interrupt.

TX PBUR 23 0b Sets the Transmit Packet Buffer Unrecoverable Error Interrupt.

RX DHER 24 0b Sets the Rx Descriptor Handler Error Interrupt.

TX DHER 25 0b Sets the Tx Descriptor Handler Error Interrupt.

SW WD 26 0b Sets the Software Watchdog Interrupt.

Reserved 27 0b Reserved.

OUTSYNC 28 0b Sets the DMA Tx Out of Sync Interrupt.

Reserved 31:29 0000b Reserved.