PCI Power Management Registers — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 201

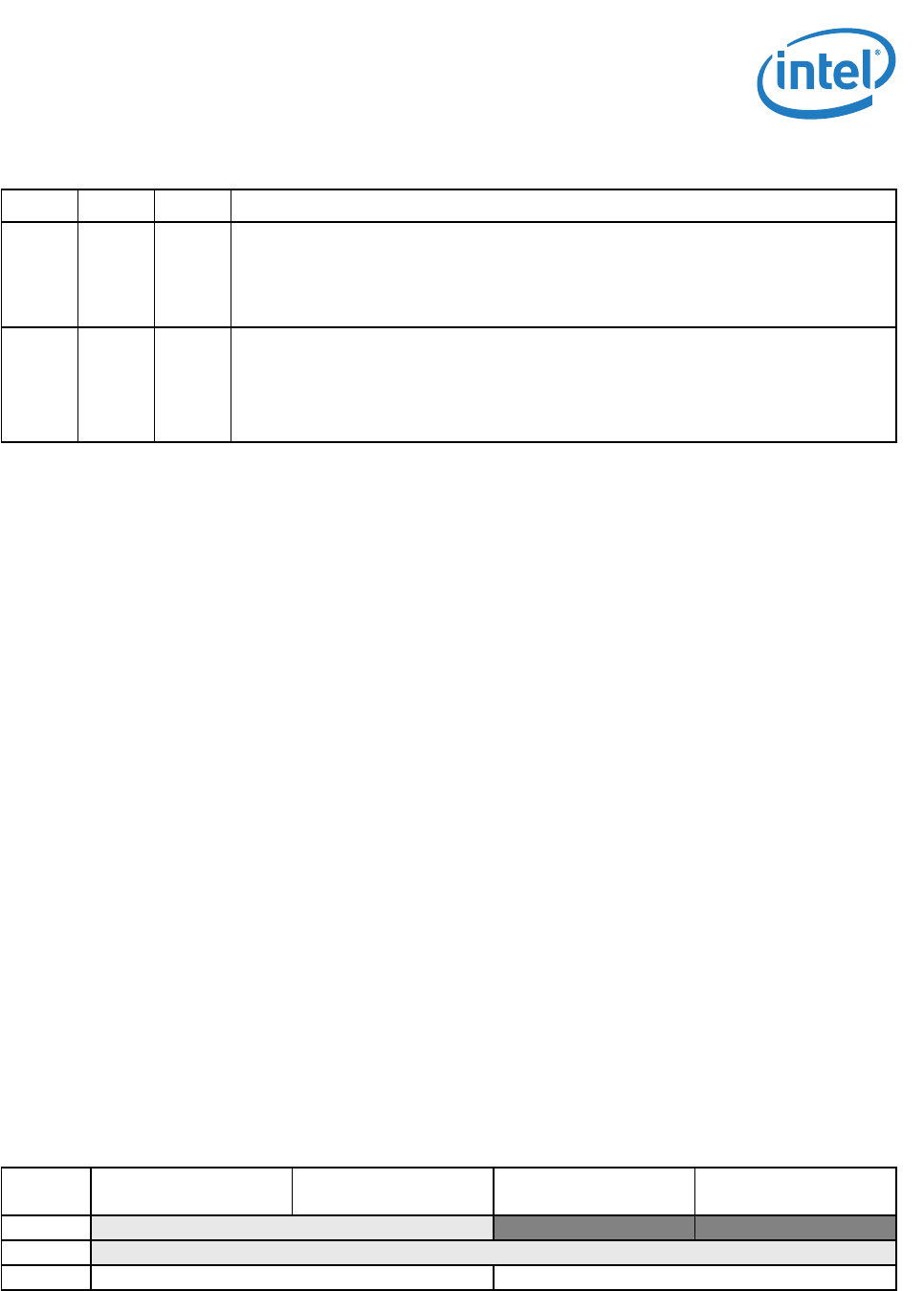

Table 71. MSI-X PBA Table Offset

To request service using a given MSI-X Table entry, a function performs a DWORD memory write

transaction using the contents of the Message Data field entry for data, the contents of the Message

Upper Address field for the upper 32 bits of address, and the contents of the Message Address field

entry for the lower 32 bits of address. A memory read transaction from the address targeted by the

MSI-X message produces undefined results.

MSI-X Table entries and Pending bits are each numbered 0 through N-1, where N-1 is indicated by the

Table Size field in the MSI-X Message Control register. For a given arbitrary MSI-X Table entry K, its

starting address can be calculated with the formula:

• Entry starting address = Table base + K*16

For the associated Pending bit K, its address for QWORD access and bit number within that QWORD can

be calculated with the formulas:

• QWORD address = PBA base + (K div 64)*8

• QWORD bit# = K mod 64

Software that chooses to read Pending bit K with DWORD accesses can use these formulas:

• DWORD address = PBA base + (K div 32)*4

• DWORD bit# = K mod 32

6.6.5.3 PCIe* Configuration Registers

PCIe* provides two mechanisms to support native features:

• PCIe* defines a PCI capability pointer indicating support for PCIe*

• PCIe* extends the configuration space beyond the 256 bytes available for PCI to 4096 bytes.

The 82575 implements the PCIe* Capability Structure for Endpoint Devices as follows:

Bits Default RD/WR Description

31:3 400h RO PBA Offset

Used as an offset from the address contained by one of the function's Base Address registers to

point to the base of the MSI-X PBA. The lower 3 PBA BIR bits are masked off (set to 0b) by

software to form a 32-bit QWORD-aligned offset.

This field is read only.

2:0 3h RO PBA BIR

Indicates which one of a function's Base Address registers, located beginning at 10h in

Configuration Space, is used to map the function's MSI-X PBA into Memory Space.

The PBA BIR value definitions are identical to those for the MSI-X Table BIR.

This field is read only.

Table 72. PCIe* Configuration Registers

Byte

Offset

Byte 3 Byte 2 Byte 1 Byte 0

A0h

PCIe* Capability Register Next Pointer Capability ID

A4h

Device Capability

A8h Device Status Device Control