Intel

®

82575EB Gigabit Ethernet Controller — Flow Control

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

176 January 2011

Under certain conditions that occur when I/OAT is enabled, software knows that it is safe to transfer a

new packet into a certain buffer without snooping on the front-side bus. This scenario occurs when

software is posting a receive buffer to hardware that the CPU has not accessed since the last time it was

owned by hardware. This might happen if the data was transferred to an application buffer by the data

movement engine. As such, software should be able to set a bit in the receive descriptor indicating that

the 82575 should perform a no snoop transfer when it eventually writes a packet to this buffer.

When a non-snoop transaction is activated, the TLP header has a non-snoop attribute in the Transaction

Descriptor field. This is triggered by the NSE bit in the Receive descriptor.

6.2 Flow Control

6.2.1 Flow Control Rules

The 82575 implements only the Default Virtual Channel (VC0). A single set of credits is maintained for

VC0.

The flow control update rules are as follows:

• The 82575 maintains two credits for Non-Posted Request Data at any given time. The controller

increments the credit by one after the credit is consumed and sends an UpdateFC packet as soon as

possible. UpdateFC packets are scheduled immediately after a resource is available.

• The 82575 provides two credits for Posted Request Header. For example, two credits are given for

two concurrent target writes and two credits for Non-Posted Request Header (two concurrent target

reads). UpdateFC packets are scheduled immediately after a resource is available.

• The 82575 follows the PCIe* recommendations for frequency of UpdateFC FCPs.

6.2.2 Upstream Flow Control Tracking

The 82575 issues a master transaction only when the required flow control credits are available. Credits

are tracked for posted, non-posted and completions. The later operates against a switch.

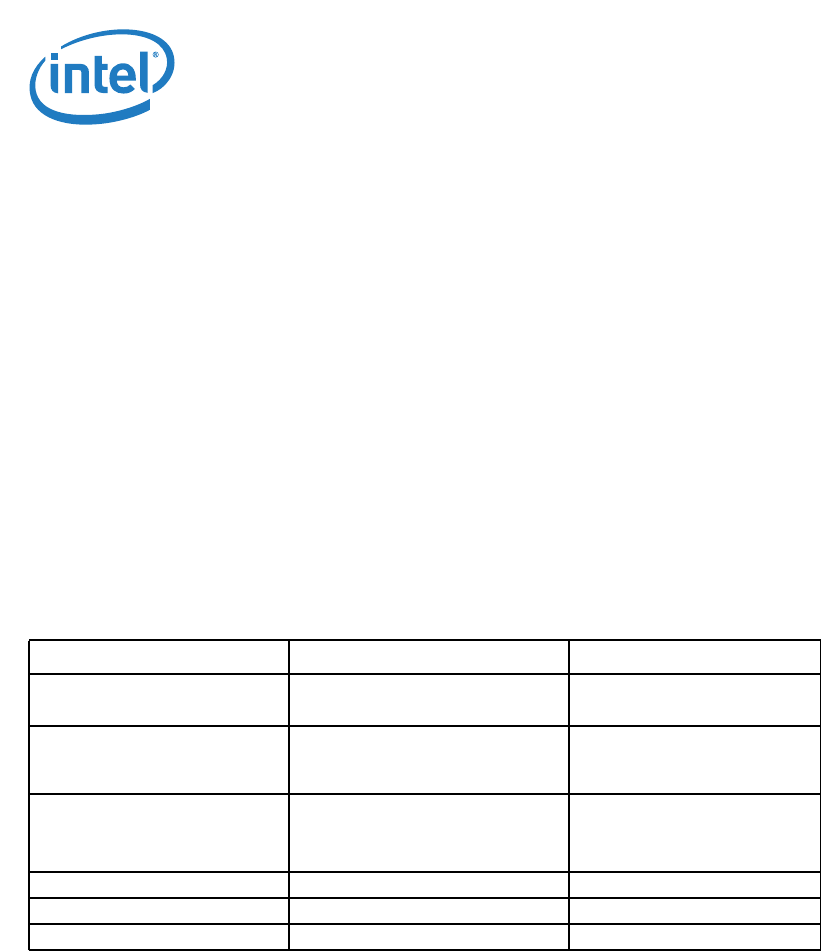

Table 53. Flow Control Credit Allocation

Credit Type Operations Number of Credits

Posted Request Header (PH) Target Write (1 unit)

Message (1 unit)

2 units (allowing concurrent

accesses to both LAN ports)

Posted Request Data (PD) Target Write (length per 16 bytes =

1)

Message (1 unit)

MAX_PAYLOAD_SIZE/16

Non-Posted Request Header

(NPH)

Target Read (1 unit)

Configuration Read (1 unit)

Configuration Write (1 unit)

2 units (allowing concurrent

target accesses to both LAN

ports)

Non-Posted Request Data (NPD) Configuration Write (1 unit) 2 units

Completion Header (CPLH) Read Completion (not applicable) Infinite (accepted immediately)

Completion Data (CPLD) Read Completion (not applicable) Infinite (accepted immediately)