Receive Descriptor Head - RDH (02810h + 100*n [n=0..3]; R/W) — Intel

®

82575EB Gigabit

Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 359

14.3.58 Receive Descriptor Head - RDH (02810h +

100*n [n=0..3]; R/W)

The value in this register might point to descriptors that are still not in host memory. As a result, the

host cannot rely on this value in order to determine which descriptor to process.

• Queue0 - RDH0 (02810h)

• Queue1 - RDH1 (02910h)

• Queue2 - RDH2 (02A10h)

• Queue3 - RDH3 (02B10h)

14.3.59 Receive Descriptor Tail - RDT (02818h + 100*n

[n=0..3]; R/W)

This register contains the tail pointers for the receive descriptor buffer. The register points to a 16-byte

datum. Software writes the tail register to add receive descriptors to the hardware free list for the ring.

• Queue0 - RDT0 (02818h)

• Queue1 - RDT1 (02918h)

• Queue2 - RDT2 (02A18h)

• Queue3 - RDT3 (02B18h)

Note: Writing the RDT register while the corresponding queue is disabled is ignored by the 82575.

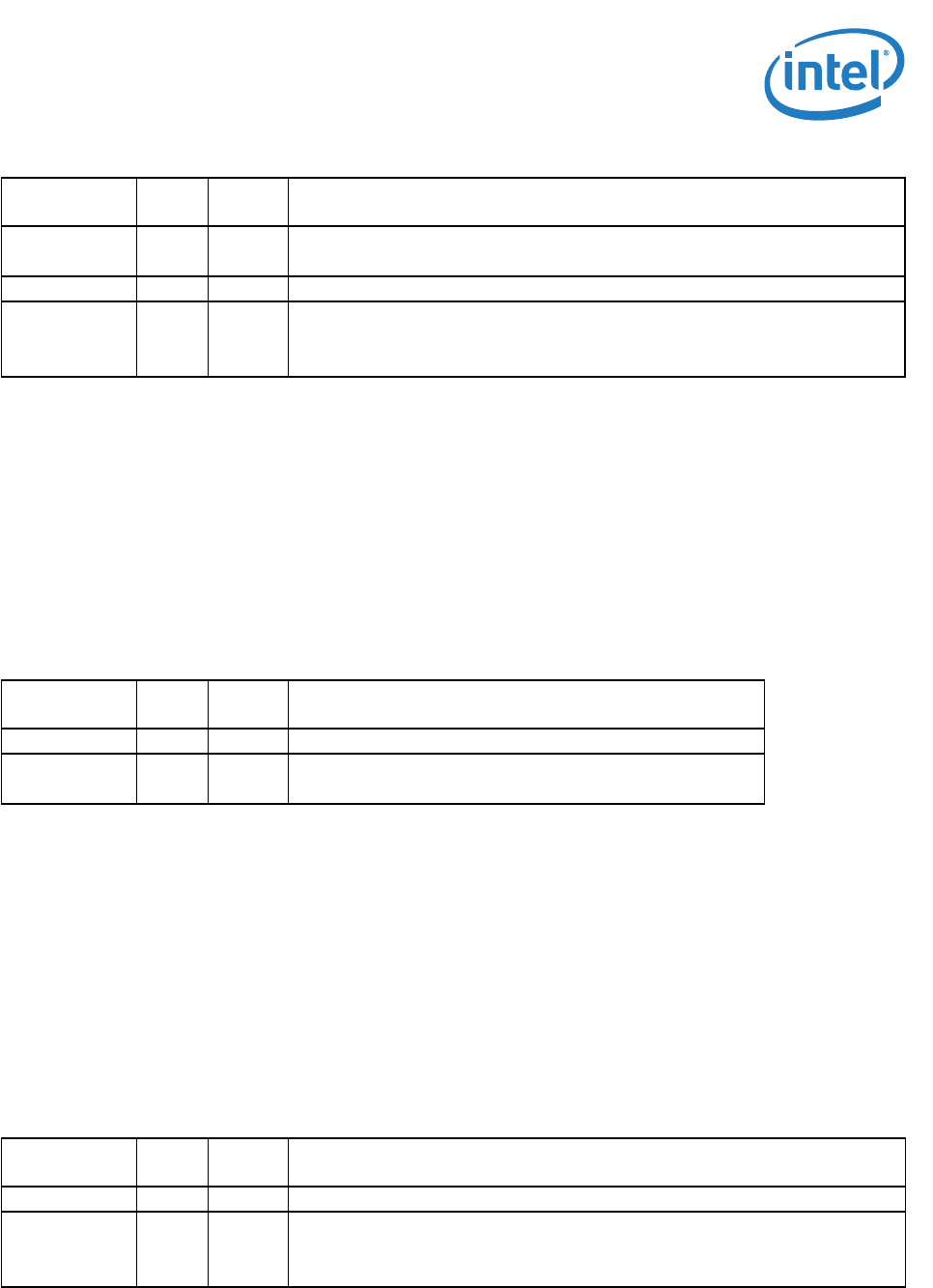

Field Bit(s)

Initial

Value

Description

Reserved 6:0 00h Ignored on writes.

Reads back as 00h.

LEN 19:7 00h Descriptor Length

Reserved 31:20 00h Reserved

Reads as 0b.

Should be written to 0b for future compatibility.

Field Bit(s)

Initial

Value

Description

RDH 15:0 0h Receive Descriptor Head

Reserved 31:16 0h Reserved

Should be written to 0b.

Field Bit(s)

Initial

Value

Description

RDT 15:0 0h Receive Descriptor Tail

Reserved 31:16 0h Reserved

Reads as 0b.

Should be written to 0b for future compatibility.