Software Semaphore - SWSM (05B50h; R/W) — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 411

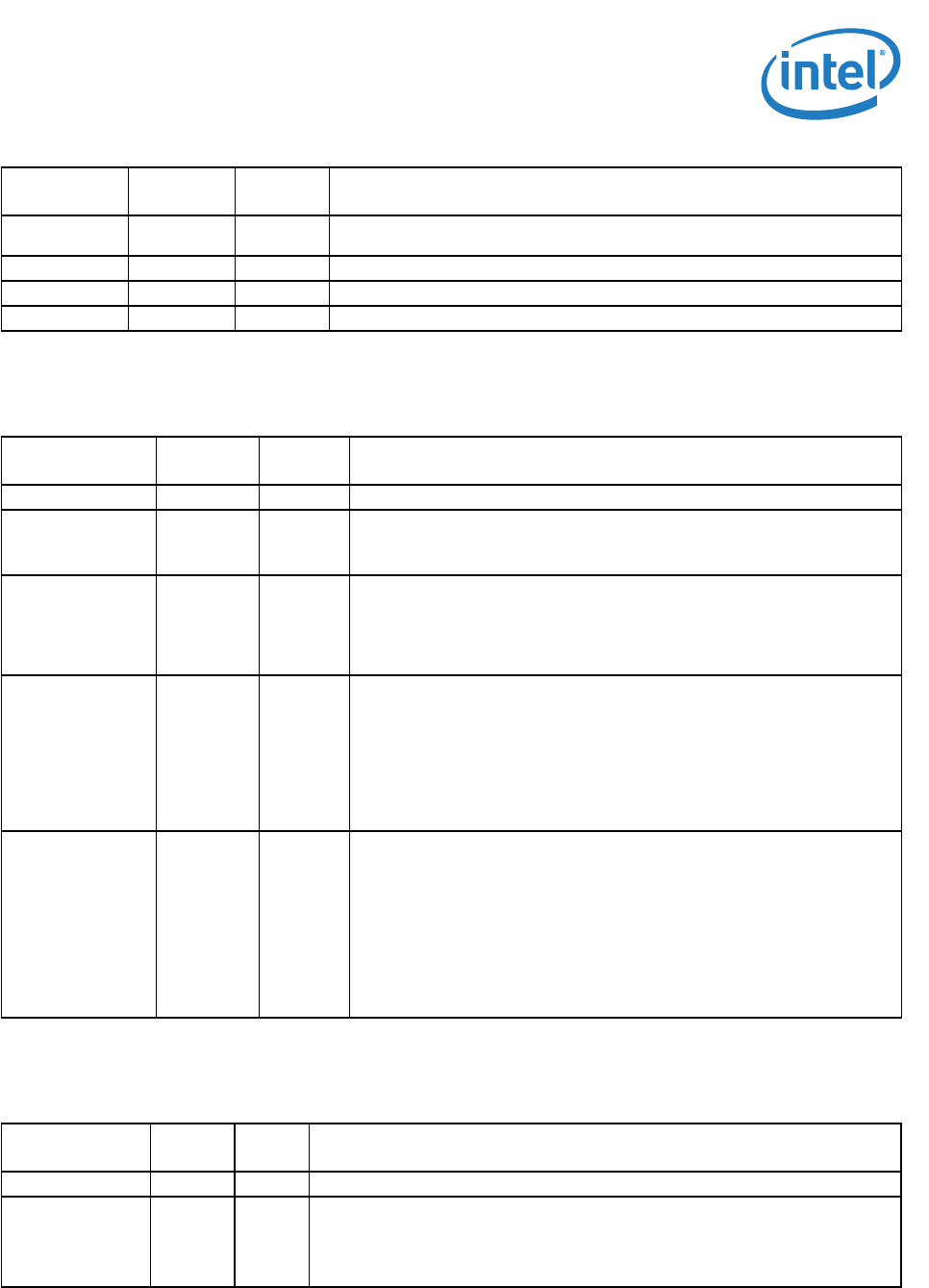

14.8.19 Software Semaphore - SWSM (05B50h; R/W)

14.8.20 Firmware Semaphore - FWSM (05B58h; R/WS)

Field Bit(s)

Initial

Value

Description

Done

Indication

31 1b When a write operation completes this bit is set to 1b indicating that new data

can be written. This bit is over written to 0b by new data.

Reserved 30:16 0b Reserved.

Address 15:8 0b Address to SerDes.

Data 7:0 0b Data to SerDes.

Field Bit(s)

Initial

Value

Description

Reserved 31:4 0h Reserved

EEUR 3 0h EEPROM Update Request

EEPROM request update from firmware. Software should clear this bit after

the FWSMFW_valid bit is set.

WMNG (SC) 2 0h Wake MNG clock

When this bit is set, hardware wakes the MNG clock (if gated).

Asserting this bit does not clear the CFG_DONE bit in the EEMNGCTL register.

This bit is self cleared on writes.

SWESMBI 1 0h Software EEPROM Semaphore bit

This bit should be set only by the device driver (read only to firmware). The

bit is not set if bit 0 in the FWSM register is set.

The device driver should set this bit and than read it to see if it was set. If it

was set, it means that the device driver can read/write from/to the EEPROM.

The device driver should clear this bit after completing EEPROM access.

Hardware clears this bit on PCIe* reset.

SMBI (RS) 0 0h Semaphore Bit

This bit is set by hardware when this register is read by the device driver and

cleared when the HOST driver writes a 0b to it.

The first time this register is read, the value is 0b. In the next read the value

is 1b (hardware mechanism). The value remains 1b until the software device

driver clears it.

This bit can be used as a semaphore between the two device's drivers in the

82575.

This bit is cleared on PCIe* reset.

Field Bit(s)

Initial

Value

Description

Reserved 31:29 0h Reserved.

Unlock_EEP 28 0h Unlock EEPROM

Set to 1b by software in order to allow re-writing to EEPROM word 12h (EEPROM

Sizing and Protection).

Cleared by firmware once EEPROM word 12h is unlocked.