Intel

®

82575EB Gigabit Ethernet Controller — Data Alignment

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

174 January 2011

6.1.3 Data Alignment

6.1.3.1 4 KB Boundary

Requests must not specify an address/length combination causing memory space access to cross a 4

KB boundary. It is the hardware responsibility to break requests into 4 KB aligned requests if required.

This does not create any software requirement. However, if software allocates a buffer across the 4 KB

boundary, hardware issues multiple requests for the buffer. Software should align buffers to the 4 KB

boundary in cases where it improves performance.

The general rules for packet alignment are as follows. Note that these apply to all 82575 requests

(read/write, snoop and no snoop):

• The length of a single request does not exceed the PCIe* limit of MAX_PAYLOAD_SIZE for write and

MAX_READ_REQ for read

• The length of a single request does not exceed 82575’s internal limitations of 256 bytes for write

and 512 bytes for read.

• A single request does not span across different memory pages as noted by the 4 KB boundary.

If a request can be sent as a single PCIe* packet and still meet the general rules for packet alignment,

then it is not broken at the cacheline boundary but rather sent as a single packet However, if the

general rules require that the request is broken into two or more packets, then the request is broken at

cacheline boundary.

6.1.4 Transaction Attributes

6.1.4.1 Traffic Class and Virtual Channels

The 82575 only supports Traffic Class 0 (default) and Virtual Channel 0 (default).

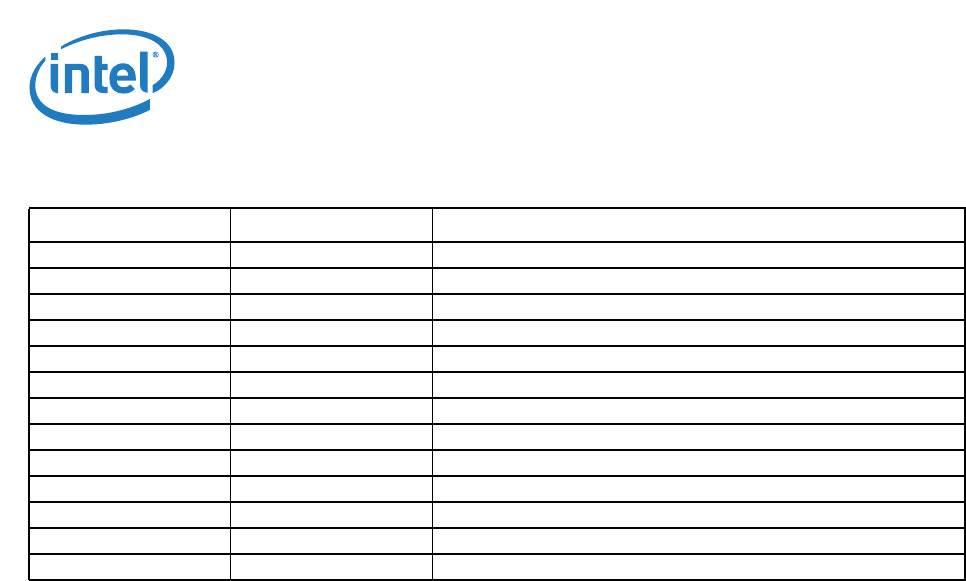

Table 51. Supported Messages on the Transmit Side

Message Code [7:0] Routing r2r1r0 Description

20h 100 Assert INT A

21h 100 Assert INT B

22h 100 Assert INT C

23h 100 Assert INT D

24h 100 De-assert INT A

25h 100 De-assert INT B

26h 100 De-assert INT C

27h 100 De-assert INT D

30h 000 ERR_COR

31h 000 ERR_NONFATAL

33h 000 ERR_FATAL

18h 000 PM_PME

1Bh 101 PME_to_Ack