PHY Registers — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 323

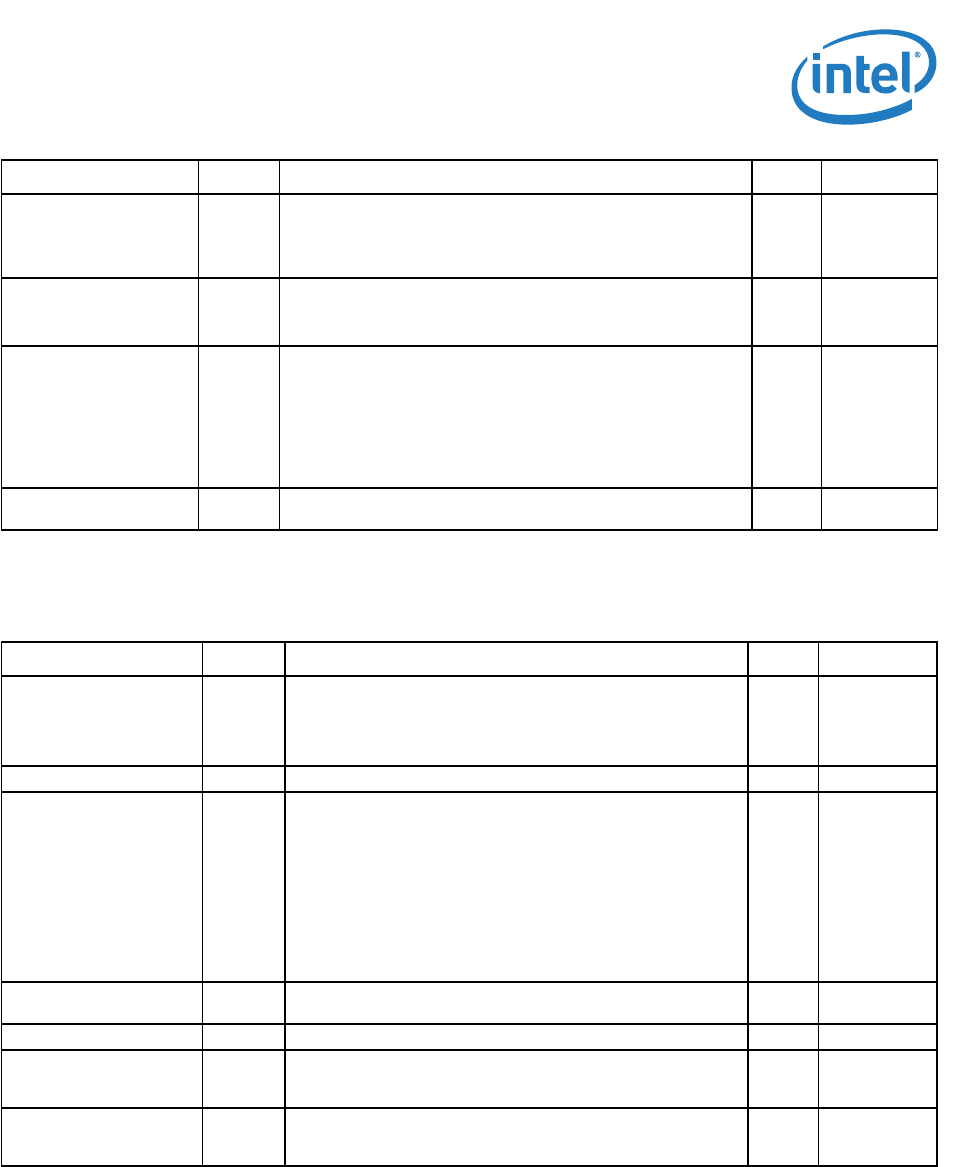

14.3.8.17 1000Base-T FIFO Register - PFIFO (20d; R/W)

Gigabit Master

Resolution

12 Gig has resolved to master. This is a duplicate of PHY register

10d, bit 14.

Programmers must read PHY register 10d, bit 14 to clear this

bit.

RO 0b

Gigabit Master Fault 13 A fault has occurred with the gig master/slave resolution

process. This is a copy of PHY register 10, bit 15.

Programmers must read PHY register 10, bit 15 to clear this bit.

RO 0b

Gigabit Scrambler Error 14 1b indicates that the PHY has detected gigabit connection errors

that are most likely due to a non-IEEE compliant scrambler in

the link partner.

0b = Normal scrambled data.

Definition is: If an_enable is true and in Gigabit mode, on the

rising edge of internal signal link_fail_inibit timer_done, the

dsp_lock is true but loc_rcvr_OK is false.

RO 0b

SS Downgrade 15 Smart Speed has downgraded the link speed from the

maximum advertised.

RO/LH 0b

Field Bit(s) Description Mode Default

Buffer Size 3:0 An unsigned integer that stipulates the number of write clocks

to delay the read controller after internal 1000Base-T’s tx_en

is first asserted. This buffer protects from underflow at the

expense of latency. The maximum value that can be set is 13d

or Dh.

R/W 0101b

Reserved 7:4 Always read as 0b. Write to 0b for normal operation. R/W 0000b

FIFO Out Steering 9:8 00b, 01b: Enable the output data bus from 1000Base-T FIFO

to transmitters, drives zeros on the output loop-back bus from

1000Base-T FIFO to external application and to DSP RX-FIFOs

in test mode.

10b: Drive zeros on output bus from 1000Base-T FIFO to

transmitters, enable data on the output loop-back bus from

1000Base-T FIFO to external application and to DSP RX-FIFOs

in test mode.

11b: Enable the output data bus from 1000Base-T FIFO to

both transmitters and loop-back bus.

R/W 00b

Disable Error Out 10 When set, disables the addition of under/overflow errors to

the output data stream on internal 1000Base-T’s tx_error.

R/W 0b

Reserved 13:11 Always read as 0b. Write to 0b for normal operation. R/W 0b

FIFO Overflow 14 Status bit set when read clock that is slower than internal

1000Base-T’s gtx_clk has allowed the FIFO to fill to capacity

mid packet. Decrease buffer size.

RO/LH 0b

FIFO Underflow 15 Status bit set when read clock that is faster than internal

1000Base-T’s gtx_clk empties the FIFO mid packet. Increase

the buffer size.

RO/LH 0b

Field Bit(s) Description Mode HW Rst