Intel

®

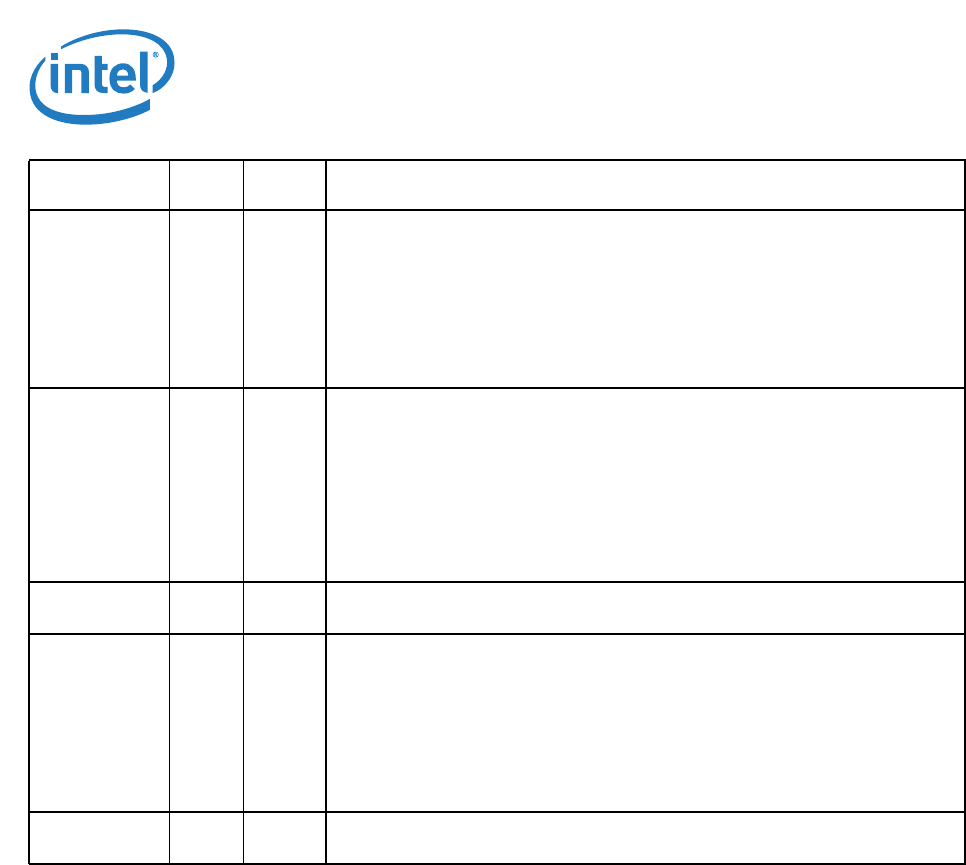

82575EB Gigabit Ethernet Controller — Split and Replication Receive Control - SRRCTL

(0280Ch + 100*n [n=0..3]; R/W)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

354 January 2011

14.3.51 Split and Replication Receive Control - SRRCTL

(0280Ch + 100*n [n=0..3]; R/W)

• Split and Replication Receive Control Register (queue 0) - SRRCTL0 (0280Ch)

• Split and Replication Receive Control Register (queue 1) - SRRCTL1 (0290Ch)

• Split and Replication Receive Control Register (queue 2) - SRRCTL2 (02A0Ch)

• Split and Replication Receive Control Register (queue 3) - SRRCTL3 (02B0Ch)

DPF 22 0b Discard Pause Frames with Station MAC Address

Controls whether pause frames directly addressed to this station are forwarded to the

host.

0b = incoming pause frames with station MAC address are forwarded to the host.

1b = incoming pause frames with station MAC address are discarded.

Note: Pause frames with other MAC addresses (for example, multicast address) are

always discarded unless the specific address is added to the accepted MAC addresses

(either multicast or unicast).

PMCF 23 0b Pass MAC Control Frames

Filters out unrecognized pause and other control frames.

0b = Pass/forward pause frames.

1b = Filter pause frames (default).

PMCF controls the DMA function of MAC control frames (other than flow control). A MAC

control frame in this context must be addressed to either the MAC control frame

multicast address or the station address, match the type field, and NOT match the

PAUSE opcode of 0001h. If PMCF = 1b then frames meeting this criteria are transferred

to host memory.

Reserved 25:24 0b0 Reserved

Should be written with 0b to ensure future compatibility.

SECRC 26 0b Strip Ethernet CRC from incoming packet

Causes the CRC to be stripped from all packets.

0b = No CRC strip.

1b = Strip CRC.

This bit controls whether the hardware strips the Ethernet CRC from the received

packet. This stripping occurs prior to any checksum calculations. The stripped CRC is

not transferred to host memory and is not included in the length reported in the

descriptor.

Reserved 31:27 0h Reserved

Should be written with 0b to ensure future compatibility.

Field Bit(s)

Initial

Value

Description