Interrupt Modes Setting Bits — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 165

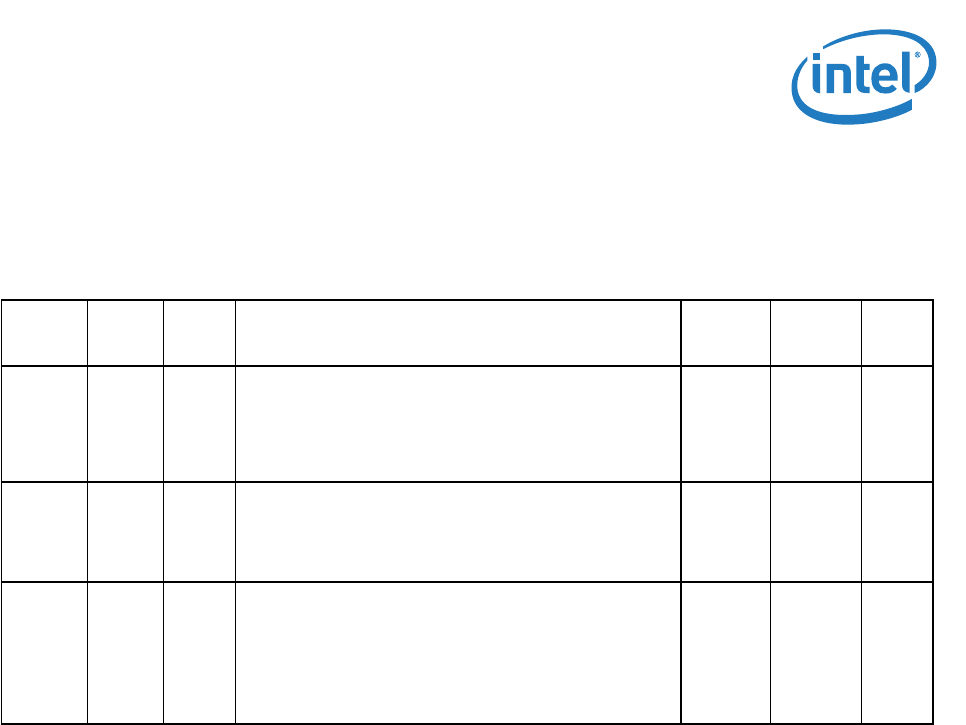

5.13.11 Interrupt Modes Setting Bits

There are bits in the CTRL_EXT register that define the behavior of the interrupt mechanism. Setting

these bits is different in each mode of operation. The following table describes the recommended

setting of these bits in the different modes:

5.14 Interrupt Moderation

An interrupt is generated upon receiving of incoming packets, as throttled by the EITR registers. There

are 10 EITR registers; each one is allocated to a vector of MSI-X.

When the MSI-X interrupt is activated, each active bit in EICR can trigger an interrupt vector. The

allocation of MSI-X vectors to each bit of EICR is set by the setting the MSI_X_ALLOC[09:0] registers.

Following the allocation, the EITR corresponding to the MSI-X vector is tied to one or more bits in EICR.

When MSI-X is not activated, the interrupt moderation is controlled by EITR[0].

Software can use EITR to limit the rate of delivery of interrupts to the host processor. This register

provides a guaranteed inter-interrupt delay between interrupts asserted by the 82575, regardless of

network traffic conditions.

The following algorithm can be used to convert the inter-interrupt interval value to the common

interrupts/sec performance metric:

interrupts/sec = (256 10

-9

sec interval)

-1

For example, if the interval is programmed to 500d, the 82575 guarantees the CPU is not interrupted

by the 82575 for at least 128 microseconds from the last interrupt. The maximum observable interrupt

rate from the 82575 should not exceed 7813 interrupts/sec.

Field Bit(s)

Initial

Value

Description

INT-x/

MSI +

Legacy

INT-x/

MSI +

Extend

MSI-X

NSICR 0 0b Non Selective Interrupt Clear on Read

When set, every read of ICR clears it. When this bit is

cleared, an ICR read causes it to be cleared only if an actual

interrupt was asserted or IMS = 0b. This bit should be

cleared by drivers not using the extended interrupts

capabilities and set otherwise.

0b

1

1. In systems where interrupt sharing is not expected, the NSICR bit can also be set by legacy drivers.

1b 1b

EIAME 24 0b Extended Interrupt Auto Mask Enable

When set (usually in MSI-X mode), upon firing of an MSI-X

message, bits set in EIAM associated with this message are

cleared. Otherwise, EIAM is used only upon read or write of

EICR/EICS registers.

0b 0b 1b

PBA_

support

31 0b PBA Support

When set, setting one of the extended interrupts masks via

EIMS causes the PBA bit of the associated MSI-X vector to

be cleared. Otherwise, the 82575 behaves in a way

supporting legacy INT-x interrupts.

Should be cleared when working in INT-x or MSI mode and

set in MSI-X mode.

0b 0b 1b