Intel

®

82575EB Gigabit Ethernet Controller — Legacy Sensor Polling Mask 1...8 Register

(F8h:FFh)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

400 January 2011

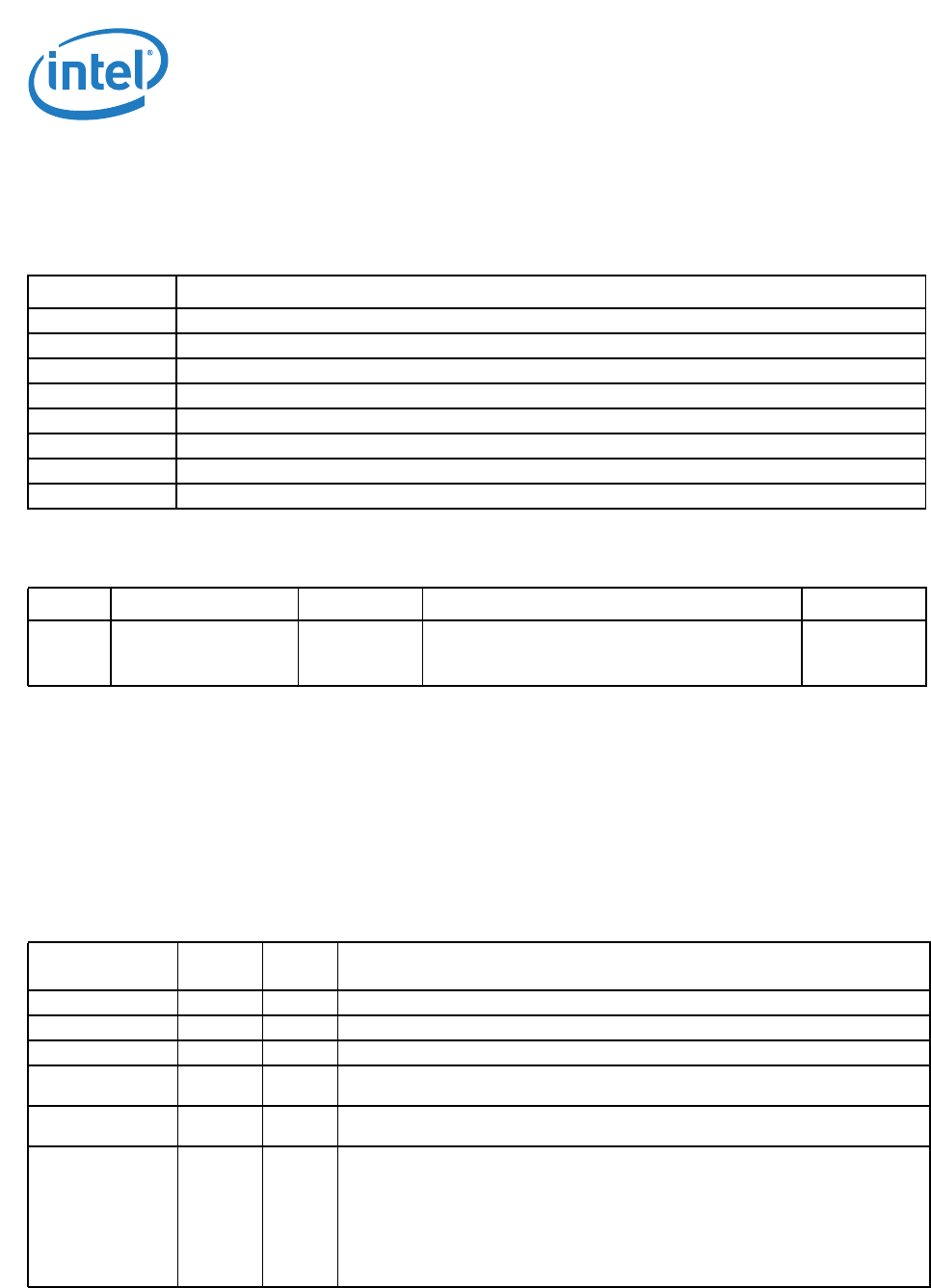

14.7.11 Legacy Sensor Polling Mask 1...8 Register

(F8h:FFh)

This register provides software an interface for the 8 legacy sensor polling data masks.

Each polling mask has the following format:

These registers are initialized to 0b after all EPROM reload events.

14.8 PCIe* Registers

14.8.1 PCIe* Control - GCR (05B00h; R)

Register Description

F8h Legacy Sensor Polling Mask #1.

F9h Legacy Sensor Polling Mask #2.

FAh Legacy Sensor Polling Mask #3.

FBh Legacy Sensor Polling Mask #4.

FCh Legacy Sensor Polling Mask #5.

FDh Legacy Sensor Polling Mask #6.

FEh Legacy Sensor Polling Mask #7.

FFh Legacy Sensor Polling Mask #8.

Bits Name Type Description / Function Default

7:0 POLL_MSK R/W Polling Mask for Polling Descriptor #N

This register is used to read and write the data mask

for Legacy Sensor Polling Descriptor #N.

0

Field Bit(s)

Initial

Value

Description

Reserved 31 0b Reserved

Self_Test_Result 30 0b If set, self test result finished successfully (after an Internal_Power_On_Reset).

GIO_Good_10s 29 0b Force good PCIe* L0s training (after an Internal_Power_On_Reset).

GIO_Dis_Rd_Err 28 0b Disable running disparity error of PCIe* 108b decoders (after an

Internal_Power_On_Reset).

L1_Act_Without_

L0s_Rx

27 0b If set, enables the 82575 to enter ASPM L1 active without any correlation of L0s_rx

(after an Internal_Power_On_Reset).

L1_Entry_Latency

(RO)

26:25 11b Determines the idle time of the PCIe* link in L0s state before initiating a transition

to L1 state. Initial value is loaded from the EEPROM.

00b - 64 s

01b - 256 s

10b - 1 ms

11b - 4 ms