Extended Interrupt Cause - EICR (01580h; RC/W1C) — Intel

®

82575EB Gigabit Ethernet

Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 345

14.3.39 Extended Interrupt Cause - EICR (01580h; RC/

W1C)

This register contains the frequent interrupt conditions for the 82575. Each time an interrupt causing

event occurs, the corresponding interrupt bit is set in this register. An interrupt is generated each time

one of the bits in this register is set and the corresponding interrupt is enabled via the Interrupt Mask

Set/Read register. The interrupt might be delayed by the selected Interrupt Throttling register.

Note that the software device driver cannot determine RxQ and TxQ bits as to what was the cause of

the interrupt:

• Receive Descriptor Write Back, Receive Queue Full, Receive Descriptor Minimum Threshold hit,

Dynamic Interrupt Moderation for Rx.

• Transmit Descriptor Write Back, Transmit Queue Empty, Transmit Descriptor Low Threshold hit for

Tx.

Writing a 1b to any bit in the register clears that bit. Writing a 0b to any bit has no effect on that bit.

Register bits are cleared on register read.

Auto clear can be enabled for any or all of the bits in this register.

14.3.40 Extended Interrupt Cause Set - EICS (01520h;

WO)

Software uses this register to set an interrupt condition. Any bit written with a 1b sets the

corresponding bit in the Extended Interrupt Cause Read register. An interrupt is then generated if one

of the bits in this register is set and the corresponding interrupt is enabled via the Extended Interrupt

Mask Set/Read register. Bits written with 0b are unchanged.

Note: In order to set bit 31 of the EICR (Other Causes), the ICS and IMS registers should be used

in order to enable one of the legacy causes.

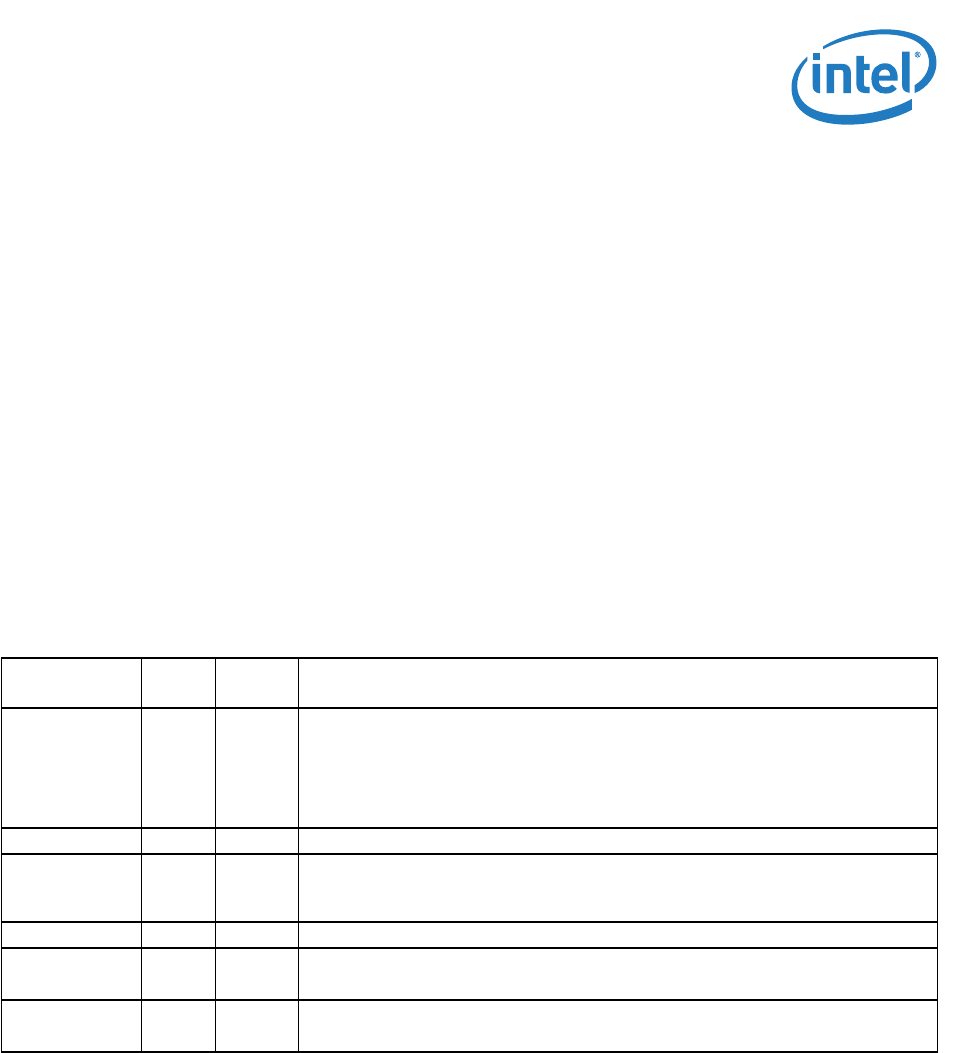

Field Bit(s)

Initial

Value

Description

RxQ 3:0 0000b Receive Queue Interrupts

One bit per receive queue, activated on receive queue events for the corresponding bit,

such as:

Receive Descriptor Write Back.

Receive Descriptor Minimum Threshold hit.

Reserved 7:4 0000b Reserved

TxQ 11:8 0000b Transmit Queue Interrupts

One bit per transmit queue, activated on transmit queue events for the corresponding

bit such as Transmit Descriptor Write Back.

Reserved 29:12 0h Reserved

TCP Timer 30 0b TCP Timer Expired

Activated when the TCP timer reaches its terminal count.

Other Cause 31 0b Interrupt Cause Active

Activated when any bit in the ICR register is set.