Hardware Accessed Words — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 67

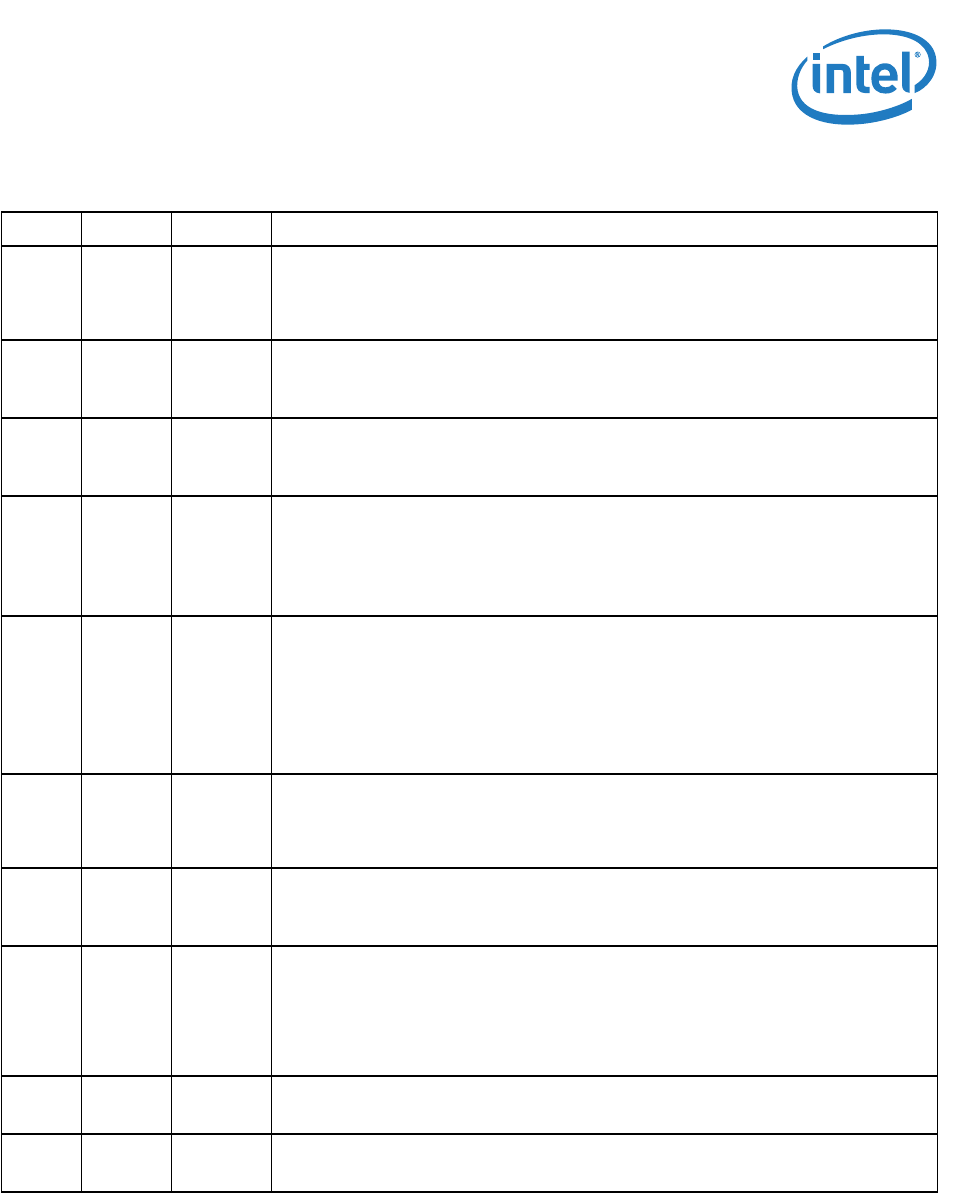

Table 16. PCIe* Initialization Configuration 3 (Word 1Ah)

Bit(s) Name Default Description

15 Master

Enable

1b When this bit is set to 1b, the PHY can act as a master (upstream component with cross

link functionality).

0b = Disable.

1b = Enable.

14 Scramble

Disable

0b When this bit is set to 1b, the PCIe* LFSR scrambling feature is disabled.

0b = Enable.

1b = Disable.

13 Ack/Nak

Scheme

0b This field identifies the acknowledgement/no acknowledgement scheme for the 82575.

0b = Scheduled for transmission following any TLP.

1b = Scheduled for transmission according to time-outs specified in the PCIe* specification.

12 Cache

Line Size

0b This bit represents the cache line size.

0b = 64 bytes.

1b = 128 bytes.

Note: The value loaded must be equal to the actual cache line size used by the platform as

configured by system software.

11:10 GIO

Capabilit

y

01b PCIe* Capability Version

The value of this field is reflected in the two LSBs of the capability version in the PCIe* CAP

register (configuration space - A2h).

Note that this is not the PCIe* version. It is the PCIe* capability version. This version is a

field in the PCIe* capability structure and is not the same as the PCIe* version. It changes

only when the content of the capability structure changes. For example, PCIe* 1.0, 1.0a

and 1.1 all have a capability version of 1. PCIe* 2.0 has a version 2 because it added

registers to the capabilities structures.

9 IO

Support

1b This bit represents the status of I/O support (I/O BAR request). When it is set to 1b, I/O is

supported.

0b = Not supported.

1b = Supported.

8 Max

Packet

Size

1b This bit identifies the status of the default packet size.

0b = 128 bytes.

1b = 256 bytes.

7:6 Lane

Width

10b This field identifies the maximum link width.

00b = 1 lane.

01b = 2 lanes.

10b = 4 lanes.

11b = Reserved.

5 Elastic

Buffer

Diff1

0b When this bit is set to 1b, the elastic buffers are activated in a more limited mode (read

and write pointers).

4 Elastic

Buffer

Control

0b When this bit equals 1b, the elastic buffers operate under phase-only mode during

electrical idle states.