Tx Completions Head Write-Back — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 161

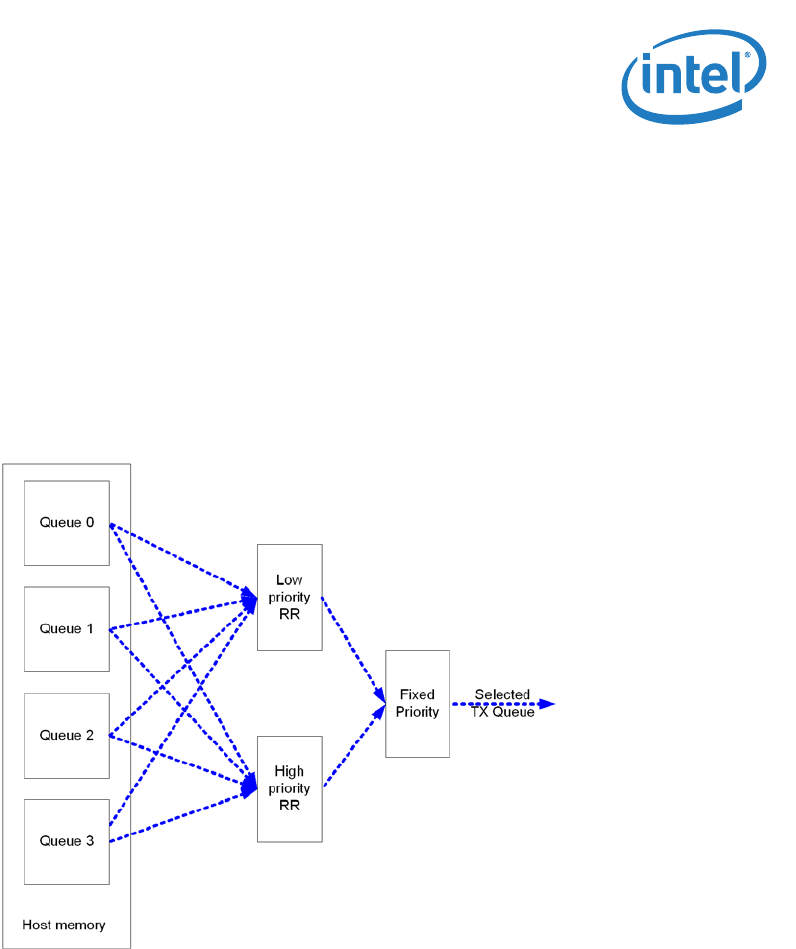

• Round robin arbitration is performed among the LP queues.

Note: In order to prevent starvation, HP queues should not be used for TSO requests. Software

must enforce this; it is not enforced by the 82575.

Software should also change the priority bit only when a queue is empty and it is guaranteed that the

82575 is not engaged in fetching Tx packets for the given queue.

The following scheme avoids excessive latency of transmit packets queued simultaneously with TSO

packets. TSO packets take tens of s (or more) to transmit. A packet queued behind several TSO

packets would suffer from an additional latency of tens to hundreds of s. This is unacceptable in some

applications where low latency is a requirement.

Figure 19. Multiple Queues in Transmit

5.12 Tx Completions Head Write-Back

In legacy hardware, transmit requests are completed by writing the DD bit to the transmit descriptor

ring. This causes cache thrash since both the software device driver and hardware are writing to the

descriptor ring in host memory. Instead of writing the DD bits to signal that a transmit request is

complete, hardware writes the contents of the descriptor queue head to host memory. The software

device driver reads that memory location to determine which transmit requests are complete. In order

to improve the performance of this feature, the software device driver needs to program DCA registers

to configure which CPU will process each TX queue.

The head counter is reflected in a memory location that is allocated by software for each queue.