Intel

®

82575EB Gigabit Ethernet Controller — PCI Power Management Registers

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

204 January 2011

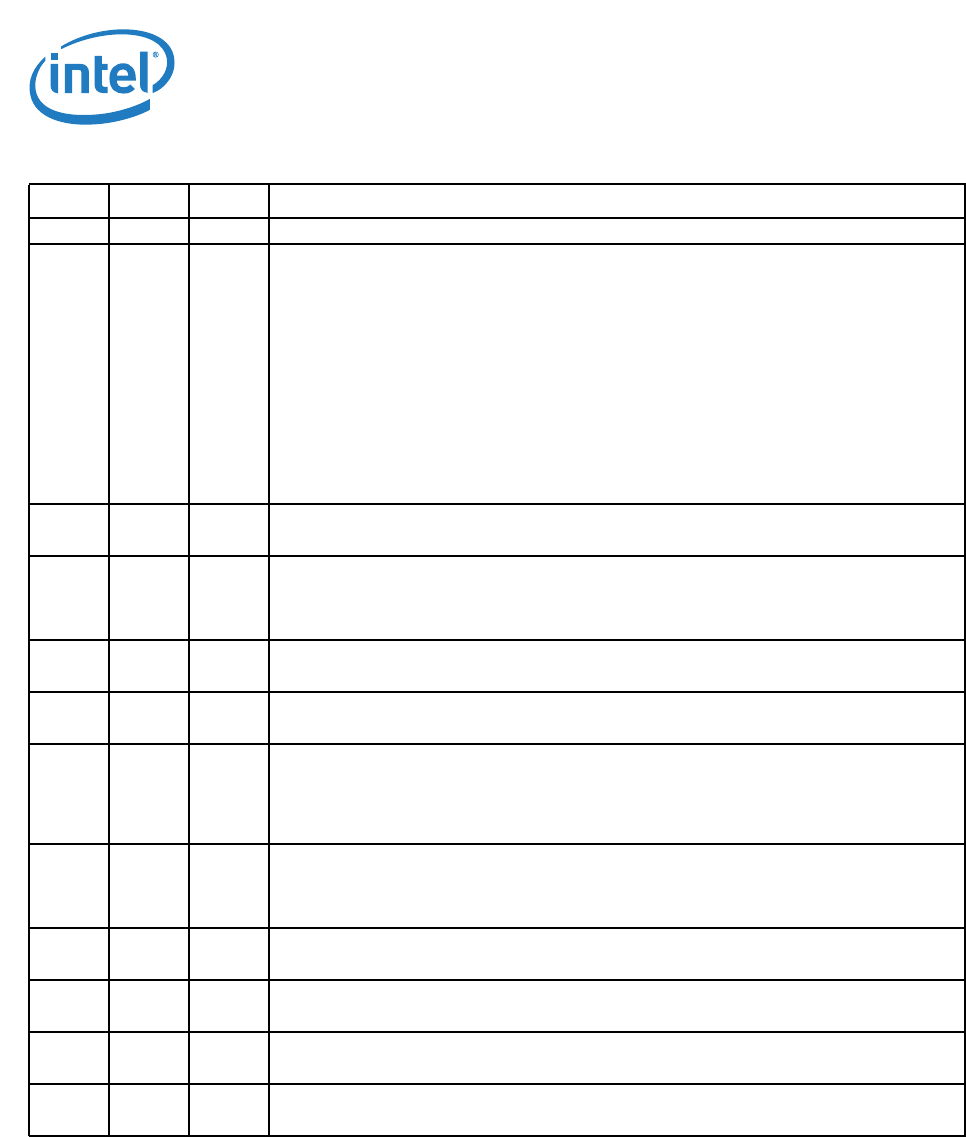

Device Status

The Device Status field is 2 bytes at offset AAh and is read only. This register provides information

about PCIe* device specific parameters. There is a dedicated register per each function.

Bit(s) RD/WR Default Description

15 RO 0b Reserved

14:12 RW 010b /

000b

Max Read Request Size

This field sets maximum read request size for the 82575 as a requester.

000b = 128 bytes. This is the default value for non-LAN functions.

001b = 256 bytes.

010b = 512 bytes. This is the default value for the LAN devices.

011b = 1 KB.

100b = 2 KB.

101b = Reserved.

110b = Reserved.

111b = Reserved.

11 RW 1b Enable No Snoop

Snoop is gated by Non Snoop bits in the GCR register in the CSR space.

10 RW 0b Auxiliary Power PM Enable

When set, the 82575 can draw auxiliary power independent of the PME AUX power signal. The

82575 is a multi-function device and is allowed to draw auxiliary power if at least one of the

functions has this bit set.

9 RW 0b Phantom Functions Enable

This field is not implemented in the 82575.

8 RW 0b Extended Tag Field Enable

This field is not implemented in the 82575.

7:5 RW 000b

(128

Bytes)

Max Payload Size

This field sets maximum TLP payload size for the 82575 functions. As a receiver, the 82575

must handle TLPs as large as the set value. As transmitter, the 82575 must not generate TLPs

exceeding the set value. The Max Payload Size supported in the 82575 capabilities register

indicates permissible values that can be programmed.

4 RW 1b Enable Relaxed Ordering

If this bit is set, the device is permitted to set the Relaxed Ordering bit in the attribute field of

write transactions that do not need strong ordering. (Documentation in the RO_DIS bit of the

CTRL_EXT register also provides more details.)

3 RW 0b Unsupported Request Reporting Enable

This bit enables error report.

2 RW 0b Fatal Error Reporting Enable

This bit enables error report.

1 RW 0b Non-Fatal Error Reporting Enable

This bit enables error report.

0 RW 0b Correctable Error Reporting Enable

This bit enables error report.