Intel

®

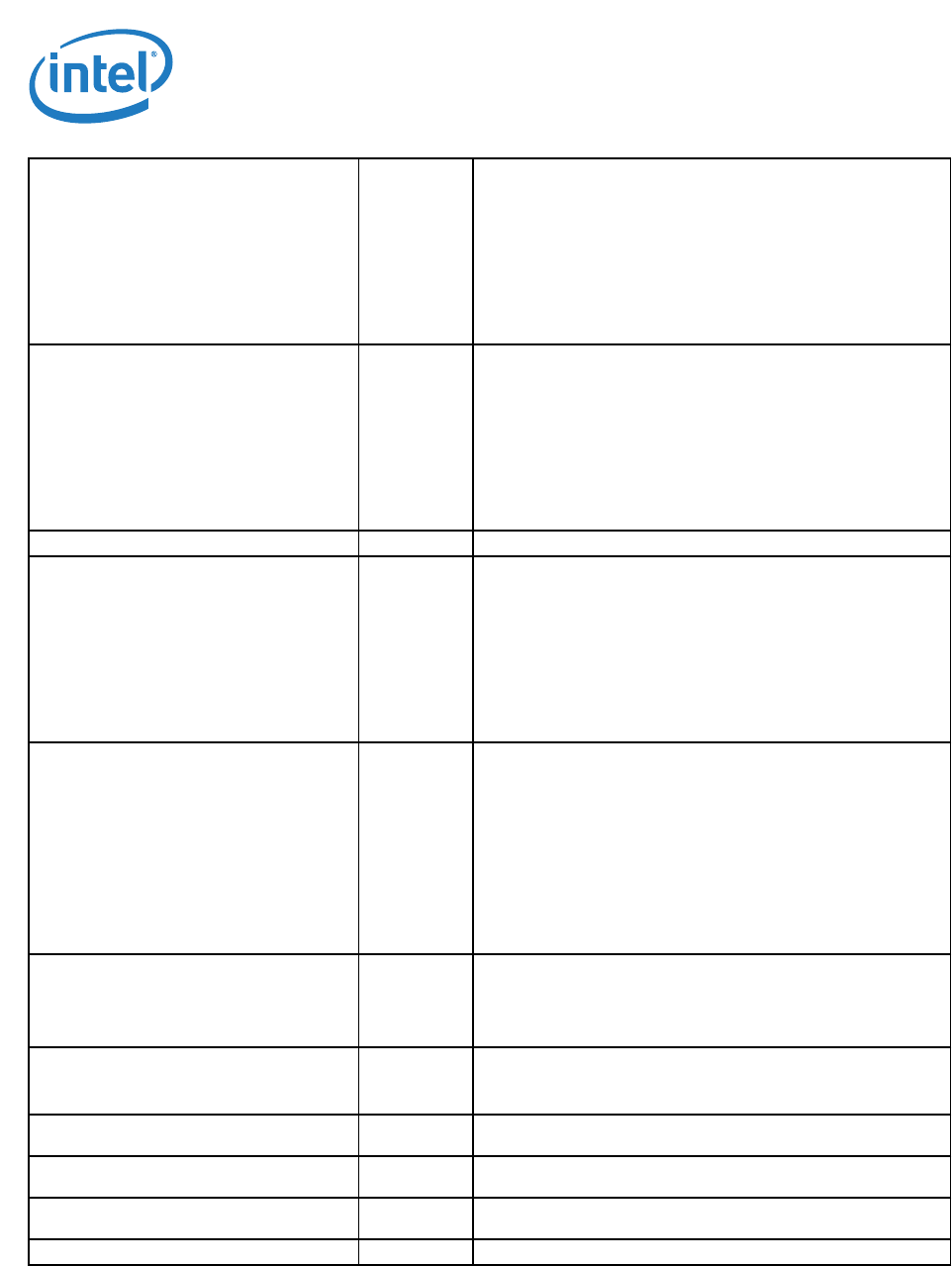

82575EB Gigabit Ethernet Controller — PCIe* Statistics Control #2 - GSCL_2 (05B14h; R)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

406 January 2011

Average latency of read request – from

initialization until end of completions.

Estimated latency is ~5 s.

40 + 41 The software will select the client need to be tested.

The statistic counter will count the number of read request of the

required client.

In addition, the accumulated time of all requests will be saved in

a time accumulator.

The average time for read request will be

[Accumulated time / Number of read requests]

(Event 41 is for the counter)

Average latency of read request RTT– from

initialization until the first completion is

arrived (Round Trip Time).

Estimated latency is 1uSec

42 + 43 The software will select the client need to be tested.

The statistic counter will count the number of read request of the

required client.

In addition, the accumulated time of all RTT will be saved in a

time accumulator.

The average time for read request will be

[Accumulated time / Number of read requests]

(Event 43 is for the counter)

Requests that reached Time Out. 44 Number of requests that reached Time Out.

Completion Latency above Threshold 45 + 46 The software will select the client need to be tested.

The software will program the required threshold (in GSCL_4 –

units of 96 ns).

One statistic counter will count the time from the beginning of

the request until end of completions.

The other counter will count the number of events.

If the time is above threshold – add 1 to the event counter.

(Event 46 is for the counter)

Completion Latency above Threshold – for

RTT

47 + 48 The software will select the client need to be tested.

The software will program the required threshold (in GSCL_4 –

units of 96 ns).

One statistic counter will count the time from the beginning of

the request until first completion arrival.

The other counter will count the number of events.

If the time is above threshold – add 1 to the event counter.

(Event 48 is for the counter)

Dwords of packet transmitted (transferred

to the physical layer), include payload and

header.

50 Include DLLP (Link layer packets) and TLP (transaction layer

packets transmitted.

Each 125 MHz cycle the counter increase in 1 (1 dw) or 2 (2 dw).

Dwords of packet received (transferred to

the physical layer), include payload and

header.

51 Include DLLP (Link layer packets) and TLP (transaction layer

packets transmitted.

Each 125 MHz cycle the counter increase in 1 (1 dw) or 2 (2 dw).

All types of DLLP packets transmitted from

link layer.

52 Each cycle, the counter increases by one, if DLLP packet was

transmitted.

Flow control DLLP transmitted from link

layer.

53 Each cycle, the counter increases by one, if message was

transmitted

Ack DLLP transmitted. 54 Each cycle, the counter increases by one, if message was

transmitted.

All types of DLLP packets received. 55 Each cycle, the counter increases by one, if DLLP was received.