Intel

®

82575EB Gigabit Ethernet Controller — PCI Power Management Registers

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

198 January 2011

Capability ID: 1 Byte, Offset 50h, (RO)

This field equals 05h indicating the linked list item as being the Message Signaled Interrupt registers.

Next Pointer: 1 Byte, Offset 51h, (RO)

This field provides an offset to the next capability item in the capability list. Its value of 60h points to

the MSI-X capability structure.

Message Control: 2 Byte, Offset 52h, (R/W)

The register fields are described in the table that follows. There is a dedicated register per PCI function

to enable separately their MSI.

Message Address Low 4 Byte, Offset 54h, (R/W)

Written by the system to indicate the lower 32 bits of the address to use for the MSI memory write

transaction. The lower two bits always return 0b regardless of the write operation.

Message Address High 4 Byte, Offset 58h, (R/W)

Written by the system to indicate the upper 32-bits of the address to use for the MSI memory write

transaction.

Message Data 2 Byte, Offset 5C, (R/W)

Written by the system to indicate the lower 16 bits of the data written in the MSI memory write DWORD

transaction. The upper 16 bits of the transaction are written as 0b.

6.6.5.2 MSI-X Configuration

The MSI-X capability structure is required for PCIe* devices. More than one MSI-X capability structure

per function is prohibited, but a function is permitted to have both an MSI and an MSI-X capability

structure.

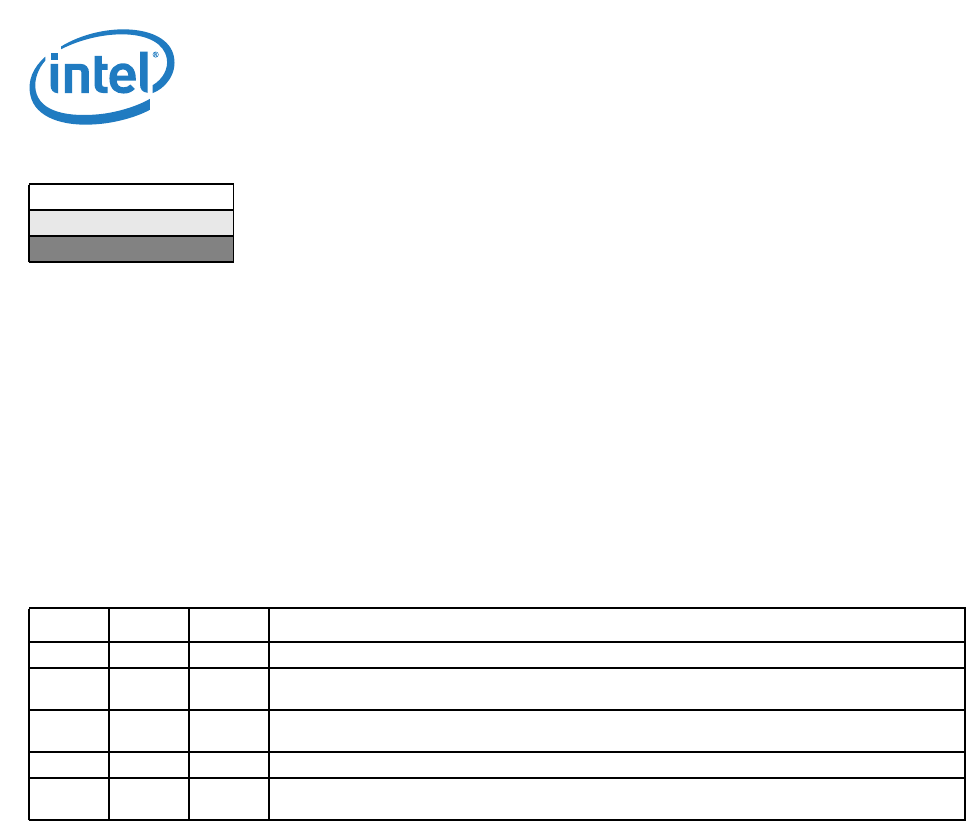

Fields identical to all functions.

Read only fields.

Hard coded fields and strapping options.

Bits Default RD/WR Description

15:8 0b RO Reserved. Reads as 0b.

7 1b RO 64-bit Capable. A value of 1b indicates that the 82575 is capable of generating 64-bit message

addresses.

6:4 000b RO Multiple Message Enable. The 82575 returns 000b to indicate that it supports a single message

per function.

3:1 000b RO Multiple Message Capable. The 82575 indicates a single requested message per each function.

0 0b R/W MSI Enable. If 1b, Message Signaled Interrupts. In this case, the 82575 generates MSI for

interrupt assertion instead of INTx signaling.