SFP 12C Parameters - I2CPARAMS (0102Ch; R/W) — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 333

14.3.21 SFP 12C Parameters - I2CPARAMS (0102Ch; R/

W)

This register is used to set the parameters for the I

2

C access to the SFP module and to allow bit bang

access to the I

2

C interface

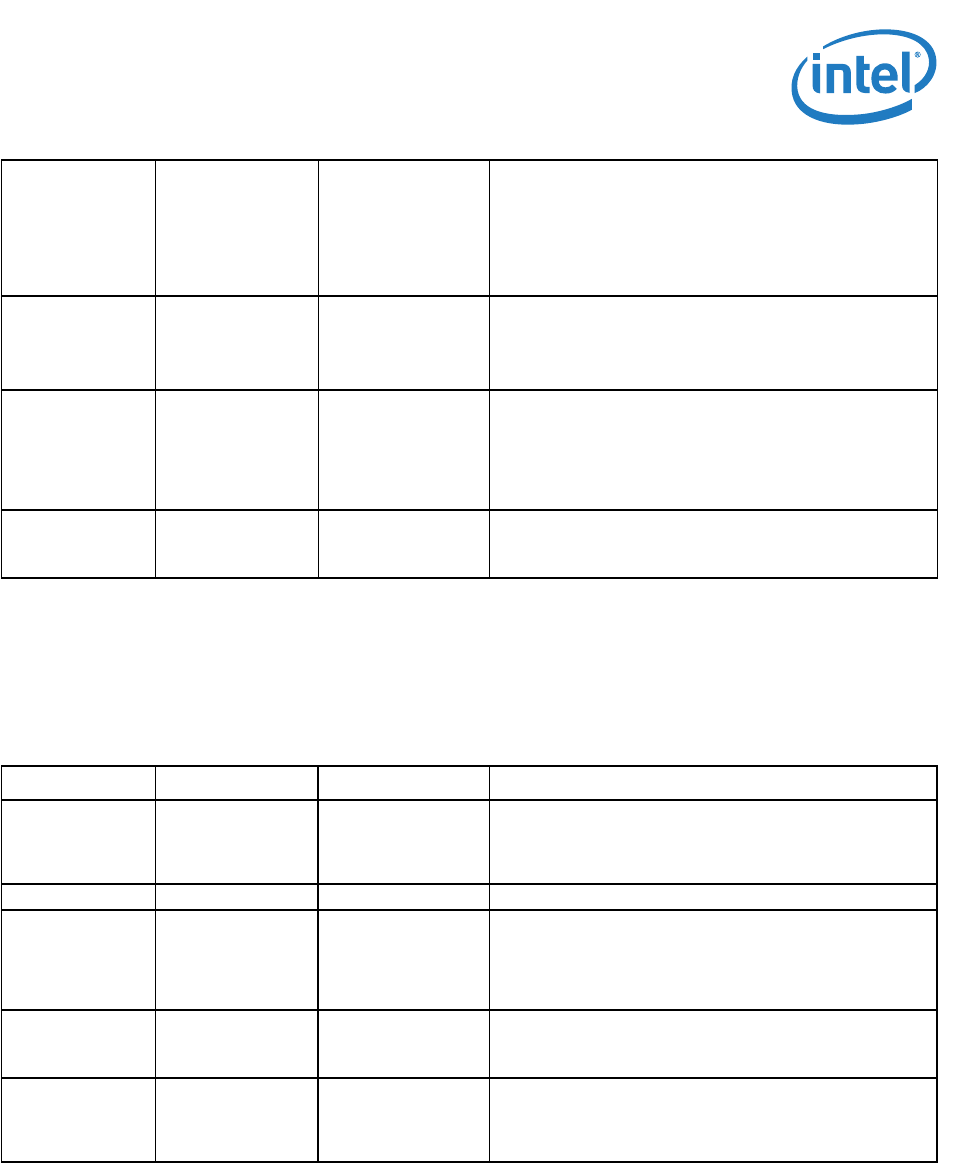

Reset 28 0b Reset Sequence

If set, sends a reset sequence before the actual read or

write.

This bit is self clearing.

A reset sequence is defined as nine consecutive stop

conditions.

R 29 0b Ready Bit

Set to 1b by the 82575 at the end of the I

2

C transaction. For

example, indicates a read or write has completed.

Reset by a software write of a command.

I 30 0b Interrupt Enable

When set to 1b by software, it causes an Interrupt to be

asserted to indicate the end of an I

2

C cycle (ICR.MDAC).

E 31 0b Error

This bit set is to 1b by hardware when it fails to complete an

I

2

C read. Reset by a software write of a command.

Field Bit(s) Initial Value Description

Write Time 4:0 110b Write Time

Defines the delay between a write access and the next

access. The value is in microseconds. A value of zero is not

valid.

Reserved 7:5 000b Reserved

I2CBB_EN 8 0b I

2

C Bit Bang Enable

If set, the I

2

C_CLK and I

2

C_DATA lines are controlled via

the CLK, DATA and DATA_OE_N fields of this register.

Otherwise, they are controlled by the hardware machine

activated via the I2CCMD or MDIC registers.

CLK 9 0b I

2

C Clock

While in bit bang mode, controls the value driven on the

I2C_CLK pad of this port.

DATA_OUT 10 0b I

2

C_DATA

While in bit bang mode and when the DATA_OE_N field is

zero, controls the value driven on the I2C_DATA pad of this

port.