Reset Operation — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 39

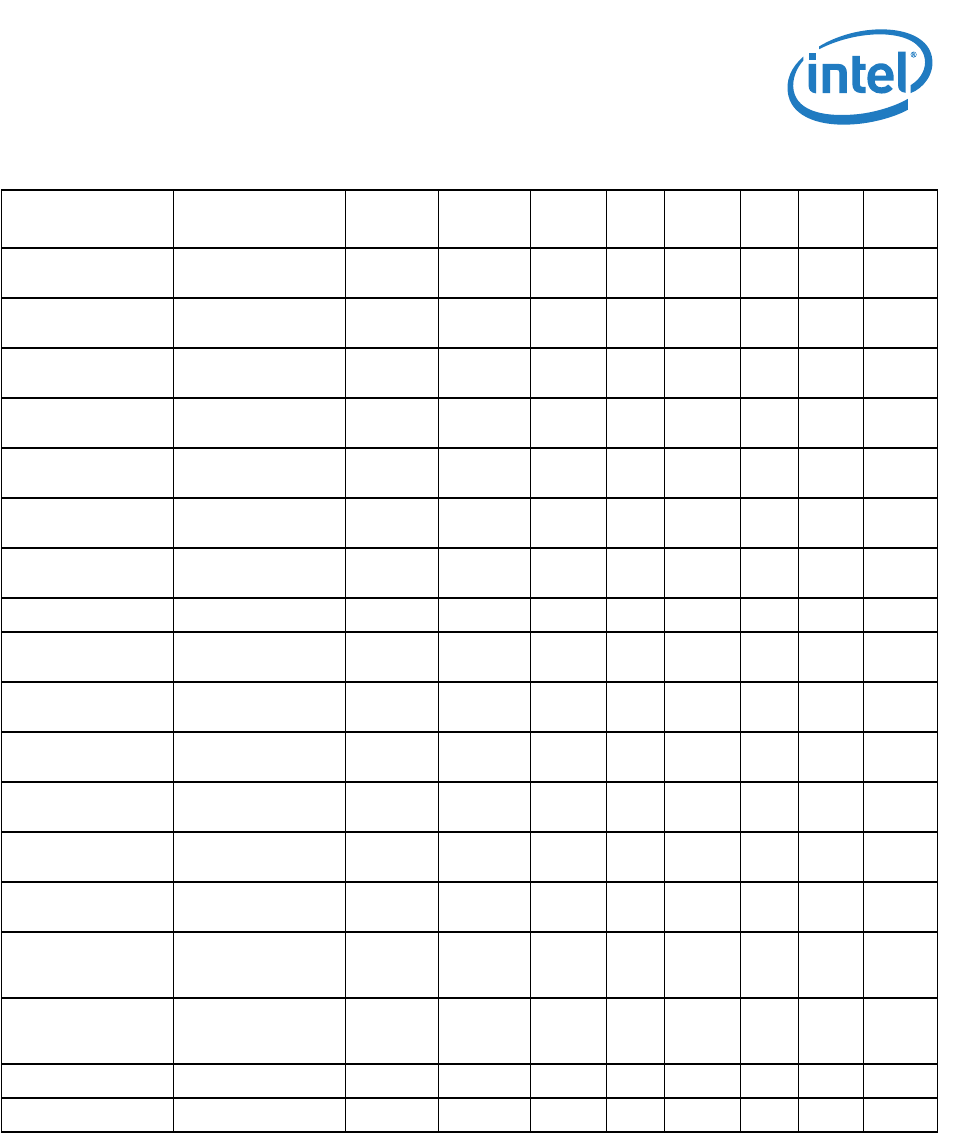

Table 3. 82575 Reset Effects

Notes:

1. If AUX_POWER = 0b the Wakeup Context is reset (PME_Status and PME_En bits should be 0b at

reset if the 82575 does not support PME from D3cold).

2. The firmware must configure the PHY after any PHY reset.

3. Link reset clears the Receive Configuration Word (RXCW).

4. The following register fields do not follow the previously stated general rules:

Reset Activation

Internal_Power_O

n_Reset

PE_

RST_N

In-Band

PCIe*

D3hot

to D0

SW

Force

TCO

EE PHY Notes

LTSSM (PCIe* back

to detect/polling)

XXX

PCIe* Link data

path

XXX

Read EEPROM (Per

Function)

XXXX

Read EEPROM

(Complete Load)

XXX

PCI Configuration

Registers RO

XXX 4

PCI Configuration

Registers RW

XXXX

PCIe* local

registers

XXX 5

Data path X X X X X X

Wake Up (PM)

Context

X Note 1 5

Wake Up Control

Register

X 6

Wake Up Status

Registers

X 7

Rule Checker

Tables

X

Manageability

Control Registers

X 8

Firmware (MMS

Unit)

X

Wake-Up

Management

Registers

X X X X X X 4, 9

Memory

Configuration

Registers

÷÷÷÷÷÷ 4

PHY/SerDes PHY ÷ ÷ ÷ ÷ ÷ ÷ 2

Strapping Pins ÷ ÷ ÷