Intel

®

82575EB Gigabit Ethernet Controller — PHY Registers

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

312 January 2011

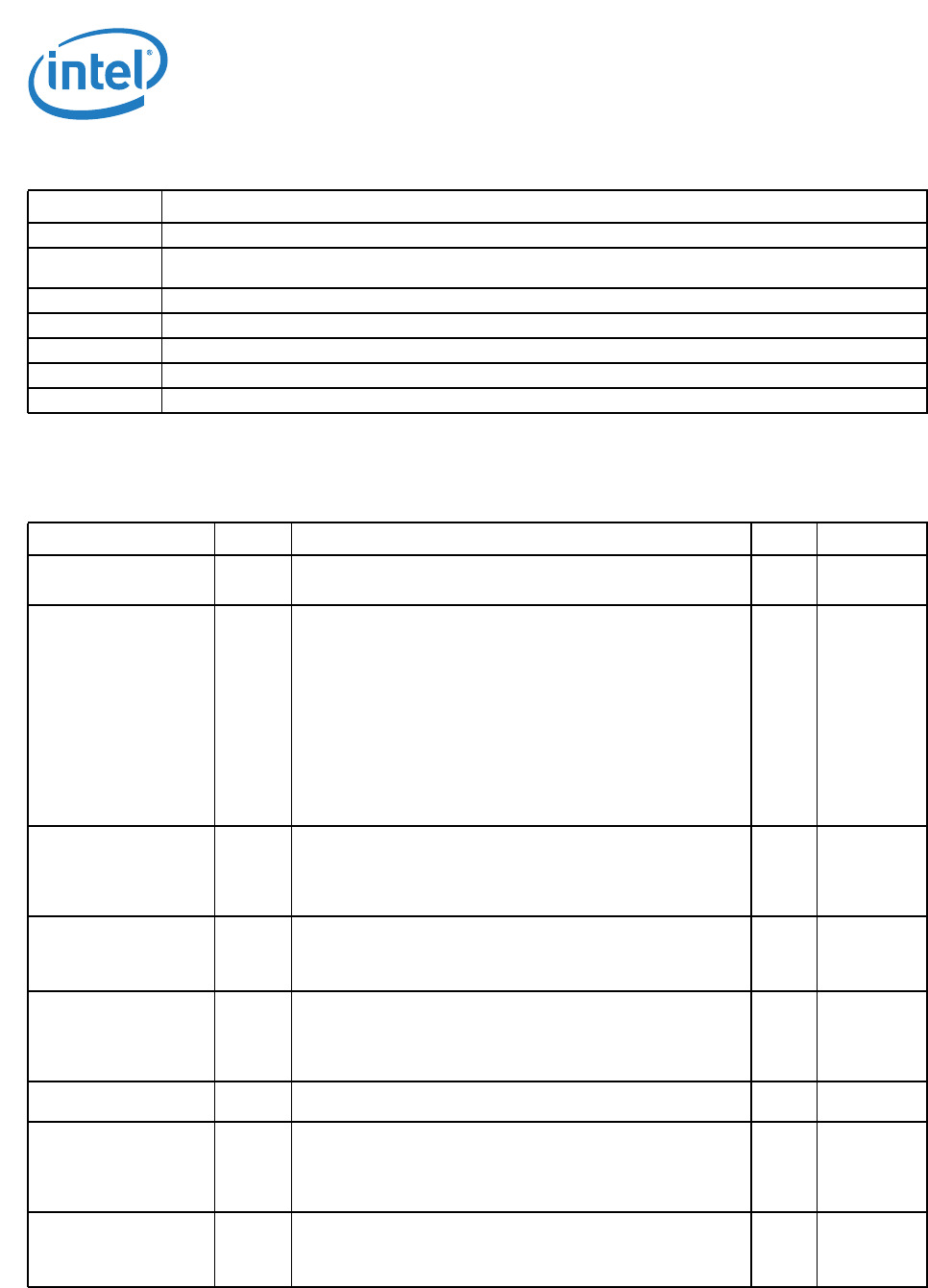

Table 89. PHY Register Bit Mode Definitions

14.3.8.1 PHY Control Register - PCTRL (00d; R/W)

Register Mode Description

LH Latched High. Event is latched and erased when read.

LL Latched Low. Event is latched and erased when read. For example, Link Loss is latched when the PHY Control

Register bit 2 = 0b. After read, if the link is good, the PHY Control Register bit 2 is set to 1b.

RO Read Only.

R/W Read and Write.

SC Self-Clear. The bit is set, automatically executed, and then reset to normal operation.

CR Clear after Read. For example, 1000BASE-T Status Register bits 7:0 (Idle Error Counter).

Update Value written to the register bit does not take effect until software PHY reset is executed.

Field Bit(s) Description Mode Default

Reserved 5:0 Reserved

Always read as 0b. Write to 0b for normal operation

RW Always

000000b

Speed Selection 1000

Mb/s (MSB)

6 Speed Selection is determined by bits 6 (MSB) and 13 (LSB) as

follows.

11b = Reserved

10b = 1000 Mb/s

01b = 100 Mb/s

00b = 10 Mb/s

A write to these bits do not take effect until a software reset is

asserted, Restart Auto-Negotiation is asserted, or Power Down

transitions from power down to normal operation.

Note: If auto-negotiation is enabled, this bit is ignored.

R/W 00b

Collision Test 7 1b = Enable COL signal test.

0b = Disable COL signal test.

Note: This bit is ignored unless loopback is enabled (bit 14 =

1b).

R/W 0b

Duplex Mode 8 1b = Full Duplex.

0b = Half Duplex.

Note: If auto-negotiation is enabled, this bit is ignored.

R/W 1b

Restart Auto-

Negotiation

9 1b = Restart Auto-Negotiation Process.

0b = Normal operation.

Auto-Negotiation automatically restarts after hardware or

software reset regardless of whether or not the restart bit is set.

WO,

SC

0b

Isolate 10 This bit has no effect on PHY functionality. Program to 0b for

future compatibility.

R/W 0b

Power Down 11 1b = Power down.

0b = Normal operation.

When using this bit, PHY default configuration is lost and is not

loaded from the EEPROM after de-asserting the Power Down bit.

R/W 0b

Auto-Negotiation Enable 12 1b = Enable Auto-Negotiation Process.

0b = Disable Auto-Negotiation Process.

This bit must be enabled for 1000BASE-T operation.

R/W 1b