PCIe* Statistics Control #3 - GSCL_3 (05B18h; R/W) — Intel

®

82575EB Gigabit Ethernet

Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 407

14.8.5 PCIe* Statistics Control #3 - GSCL_3 (05B18h;

R/W)

This counter holds the threshold values needed for some of the event counting. The event increases

only after the value passes the threshold boundary.

14.8.6 PCIe* Statistics Control #4 - GSCL_4 (05B1Ch;

R/W)

This counter holds the threshold values needed for some of the event counting. The event increases

only after the value passes the threshold boundary.

14.8.7 PCIe* Counter #0 - GSCN_0 (05B20h; R/W)

14.8.8 PCIe* Counter #1 - GSCN_1 (05B24h; R/W)

Flow control DLLP received in Link layer. 56 Each cycle, the counter increases by one, if message was

received.

Ack DLLP received. 57 Each cycle, the increases by one, if message was received.

Nack DLLP received. 58 Each cycle, the counter increases by one, if message was

transmitted

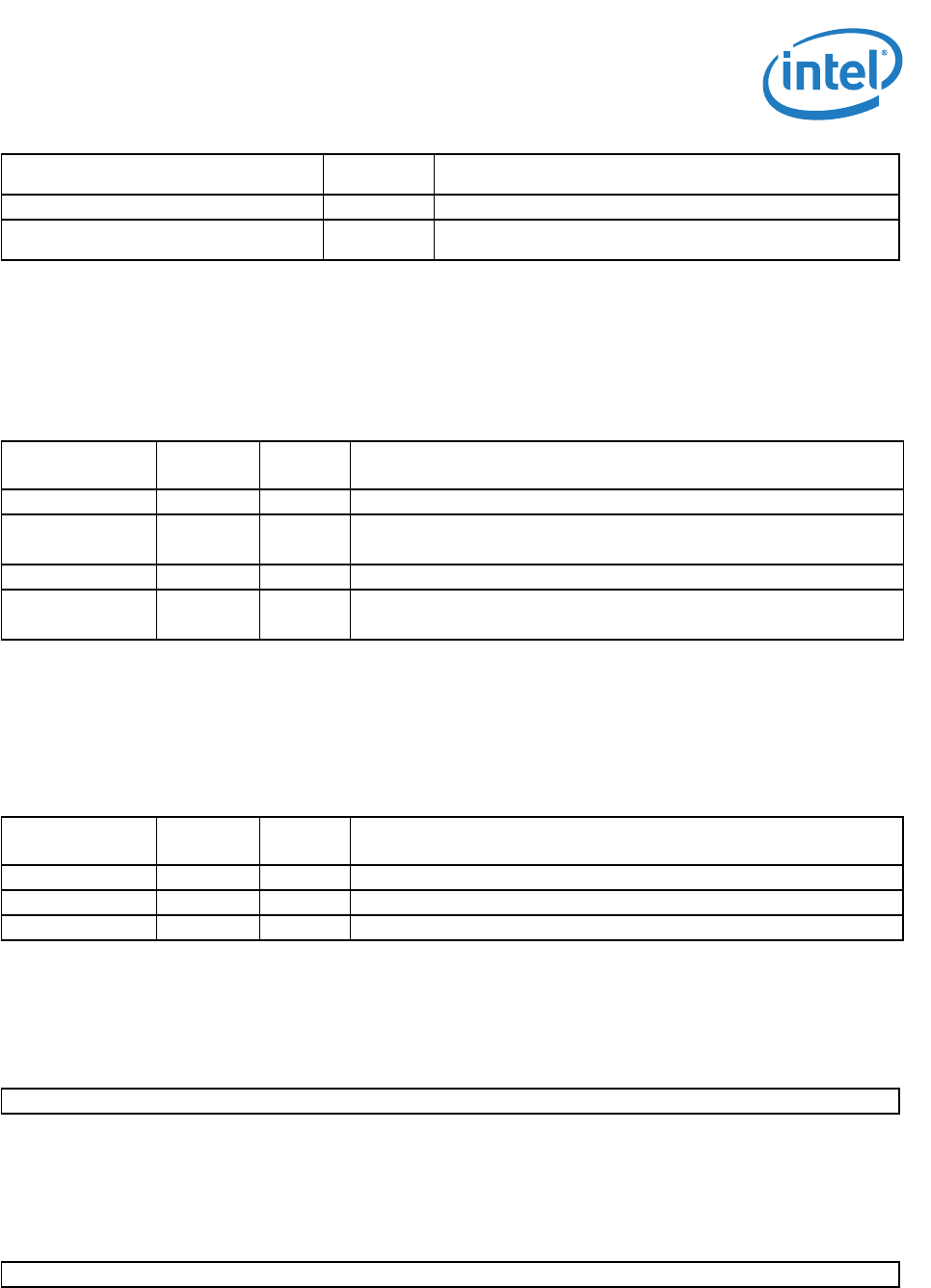

Field Bit(s)

Initial

Value

Description

Reserved 31:28 0b Reserved.

GIO_FC_TH_1 27:16 0b Threshold of flow control credits.

Optional values: 0 - (256-1).

Reserved 15:12 0b Reserved.

GIO_FC_TH_0 11:0 0b Threshold of flow control credits.

Optional values: 0 - (256-1).

Field Bit(s)

Initial

Value

Description

Reserved 31:16 0b Reserved.

GIO_RB_TH 15:10 0b Retry buffer threshold.

GIO_COML_TH 9:0 0b Completions latency threshold.

31 0

Event Counter

31 0

Event Counter