Intel

®

82575EB Gigabit Ethernet Controller — Multiple Receive Queues Command Register - MRQC

(05818h; R/W)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

382 January 2011

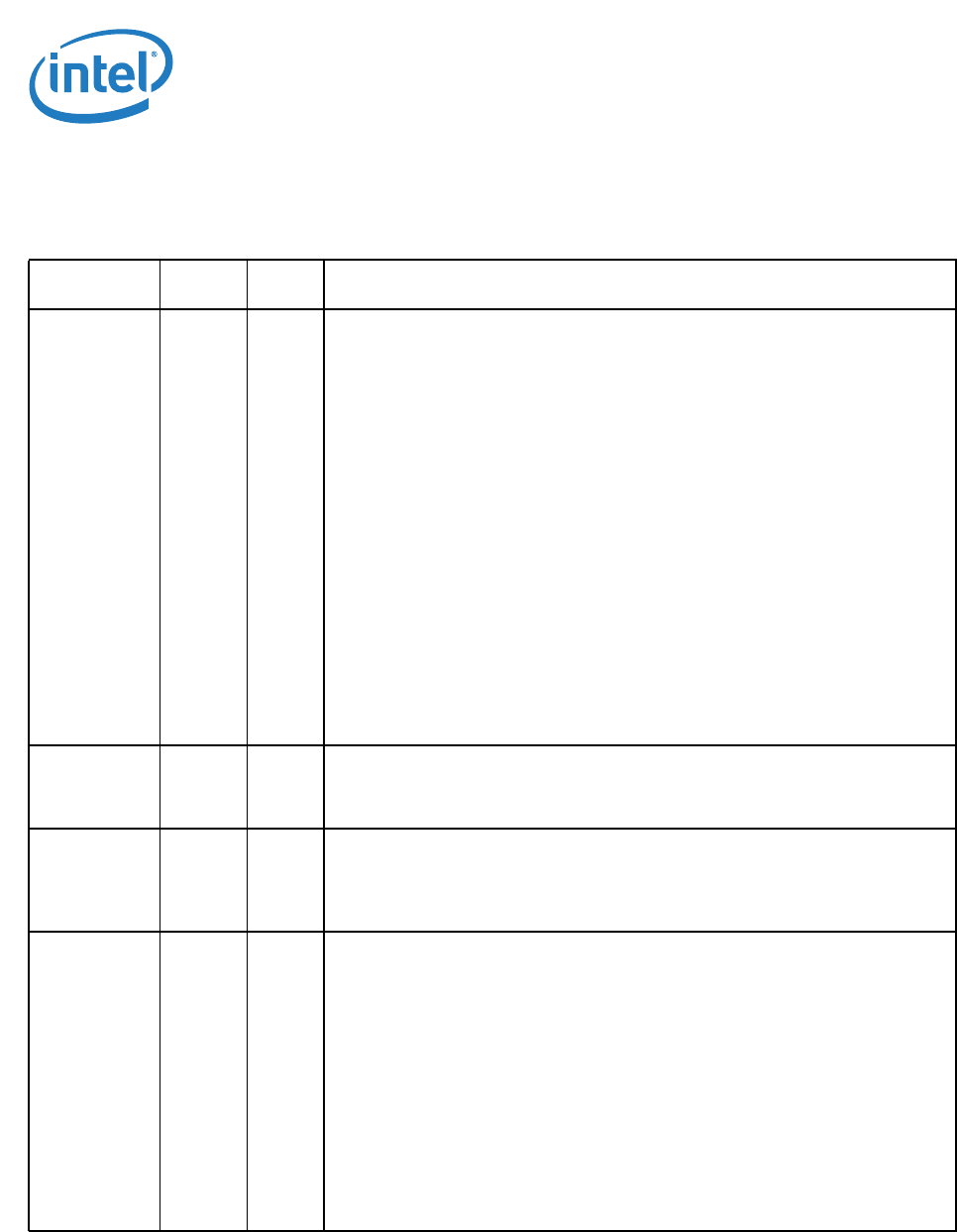

14.5.5 Multiple Receive Queues Command Register -

MRQC (05818h; R/W)

Notes:

1. MRQC_EN is used for enable/disable RSS hashing and also for enabling multiple receive queues. Disabling this feature is not

recommended. Model usage is to reset the 82575 after disabling the RSS.

2. Packet would be tagged as IPv6 if it is without any of the Home-Address-Option field and Routing-Header-Type-2 field. As a

result, if a packet is tagged with IPv6 (type 5) in this case, the device driver would have to convert it to IPv6Ex (type 4).

Field Bit(s)

Initial

Value

Description

MRQE 2:0 00h Multiple Receive Queues Enable

Enables support for Multiple Receive Queues and defines the mechanism that controls

queue allocation. Note that the RXCSUM.PCSD bit must also be set to enable Multiple

Receive Queues.

000b = Multiple Receive Queues are disabled.

001b = Reserved.

010b = Multiple receive queues as defined by RSS for four queues.

011b = Multiple receive queues as defined by VMDq based on packet destination MAC

address.

100b = Multiple receive queues as defined by VMDq based on packet VLAN tag ID.

101b = Multiple receive queues as defined by VMDq based on packet destination MAC

address and RSS.

110b = Multiple receive queues as defined by VMDq based on packet VLAN tag ID and

RSS.

111b = Reserved.

In SKUs not supporting VT, The only functional values for this field are 000b and 010b.

Writing any other value is treated as if a value of zero was written. A value other than

zero might cause unexpected results.

Note: When RSS is enabled (MRQC.MRQE equals 010b, 101b or 110b), TCP Rx

checksum must also be enabled (RXCSUM.TUOFL = 1b).

RSS Interrupt

Enable

2 0h RSS Interrupt Enable

When set, this bit enables interrupt control by the RSS Interrupt Mask register. When

cleared, a receive packet generates an interrupt indication independent of the RSS

Interrupt registers.

Reserved 15:3 0h Reserved.

RSS Field

Enable

31:16 0h Each bit, when set, enables a specific field selection to be used by the hash function.

Several bits can be set at the same time.

Bit[16] = Enable TcpIPv4 hash function

Bit[17] = Enable IPv4 hash function

Bit[18] = Enable TcpIPv6Ex hash function

Bit[19] = Enable IPv6Ex hash function

Bit[20] = Enable IPv6 hash function

Bit[21] = Enable TCPIPv6 has function

Bit[22] = Enable UDPIPv4

Bit[23] = Enable UDPIPv6

Bit[24] = Enable UDPIPv6Ext

Bits[31:25] = Reserved; set to 0b.